- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369884 > LXT312JE PCM Repeater PDF資料下載

參數(shù)資料

| 型號: | LXT312JE |

| 英文描述: | PCM Repeater |

| 中文描述: | 的PCM中繼 |

| 文件頁數(shù): | 8/26頁 |

| 文件大小: | 402K |

| 代理商: | LXT312JE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

LXT310

—

T1 CSU/ISDN PRI Transceiver

8

Datasheet

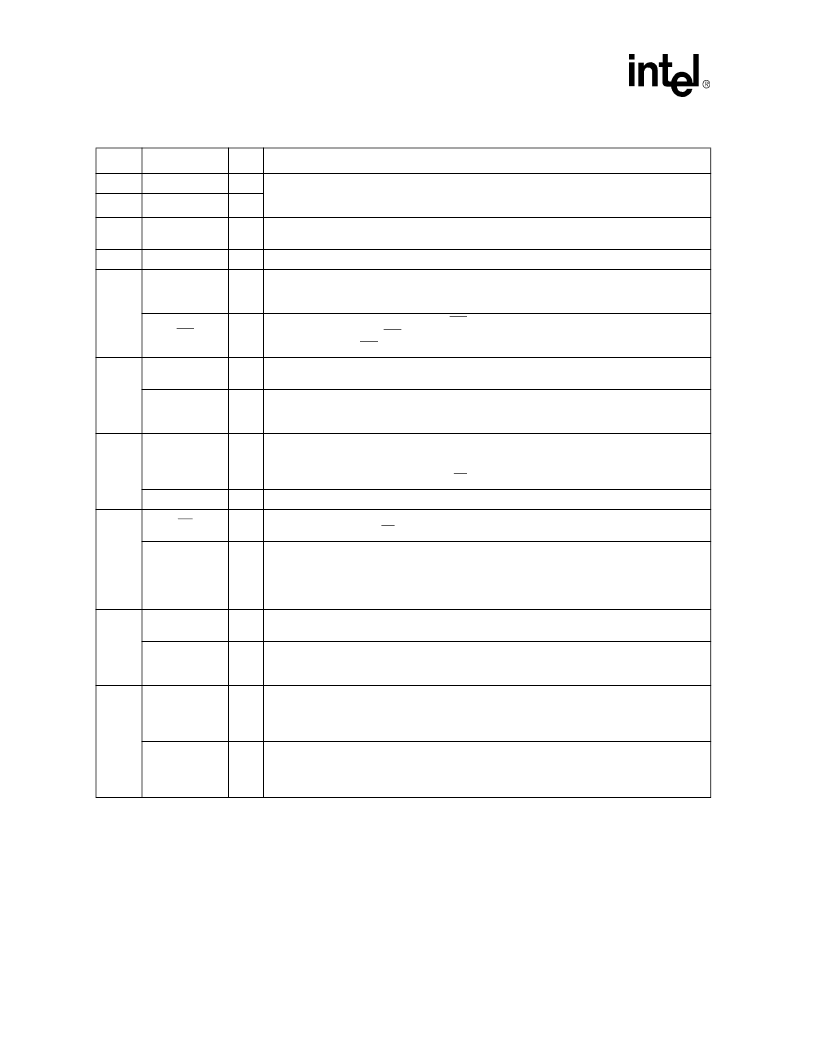

19

RTIP

I

Receive Tip; Receive Ring.

The AMI signal received from the line is applied at these pins.

A 1:1 transformer is required. Data and clock from the signal applied at these pins are

recovered and output on the RPOS/RNEG and RCLK pins.

20

RRING

I

21

RV+

–

Receive Power Supply.

+5 VDC power supply for all circuits except the transmit drivers.

(Transmit drivers are supplied by TV+.)

22

RGND

–

Receive Ground.

Ground return for power supply RV+.

23

NLOOP

O

Network Loopback

(H/W mode)

.

When High, indicates Inband Network Loopback has been

activated by reception of 00001 pattern for five seconds. NLOOP is reset by reception of 001

for five seconds, or by activation of RLOOP or LLOOP.

INT

O

Interrupt

(Host mode)

.

In Host mode INT goes Low to flag the host processor when LOS or

NLOOP changes state.

INT

is an open-drain output and should be tied to power supply RV+

through a resistor.

INT

is reset by clearing the LOS or NLOOP register bit.

24

SDI

I

Serial Data In

(Host mode)

.

The serial data input stream is applied to this pin when the

LXT310 operates in the Host mode. SDI is sampled on the rising edge of SCLK.

LBO1

I

Line Build-Out Select 1

(H/W mode)

.

In Hardware mode LBO1 works in conjunction with

LBO2 to select the transmit line build-outs: 00 = 0 dB, 01 = 7.5 dB, 10 = 15 dB, and 11 = 22.5

dB.

25

SDO

O

Serial Data Out

(Host mode)

.

The serial data from the LXT310 register is output on this pin

in Host mode. If CLKE is High, SDO is valid on the rising edge of SCLK. If CLKE is Low,

SDO is valid on the falling edge of SCLK. This pin goes to a high-impedance state when the

serial port is being written to and when

CS

is High.

LBO2

I

Line Build-Out Select 2

(H/W mode)

.

Refer to LBO1 signal description.

26

CS

I

Chip Select

(Host mode)

.

This pin selects the serial interface in the Host mode. For each

read or write operation,

CS

must transition from High to Low, and remain Low.

RLOOP

I

Remote Loopback

(H/W mode)

.

This pin controls loopback in the Hardware mode. Setting

RLOOP High enables Remote Loopback. During Remote Loopback, in-line encoders and

decoders are bypassed. Setting both RLOOP and LLOOP High, while holding TAOS Low,

causes a Reset. Setting both RLOOP and LLOOP High, with TAOS High (or tying RCLK to

RLOOP), enables Network Loopback detection.

27

SCLK

I

Serial Clock

(Host mode)

.

This clock is used in the Host mode to write data to or read data

from the serial interface registers.

LLOOP

I

Local Loopback

(H/W mode)

.

This input controls loopback functions in the Hardware mode.

Setting LLOOP High enables the Local Loopback mode. Setting both LLOOP and RLOOP

High, while holding TAOS Low, causes a Reset.

28

CLKE

I

Clock Edge Select

(Host mode)

.

Setting CLKE High causes RPOS and RNEG to be valid

on the falling edge of RCLK, and SDO to be valid on the rising edge of SCLK. When CLKE is

Low, RPOS and RNEG are valid on the rising edge of RCLK, and SDO is valid on the falling

edge of SCLK.

TAOS

I

Transmit All Ones

(H/W mode)

.

When set High in the Hardware mode, TAOS causes the

LXT310 to transmit a stream of marks at the TCLK frequency. Activating TAOS causes

TPOS and TNEG inputs to be ignored. TAOS is inhibited during Remote Loopback. Setting

TAOS, LLOOP and RLOOP High simultaneously enables Network Loopback detection.

Table 1. Pin Descriptions (Continued)

Pin #

Sym

I/O

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT312NE | PCM REPEATER|T-1(DS1)|CMOS|DIP|16PIN|PLASTIC |

| LXT312PE | PCM REPEATER|T-1(DS1)|CMOS|LDCC|44PIN|PLASTIC |

| LXT313JE | PCM Repeater |

| LXT313NE | PCM Repeater |

| LXT313PE | PCM Repeater |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT312NE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM REPEATER|T-1(DS1)|CMOS|DIP|16PIN|PLASTIC |

| LXT312PE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM REPEATER|T-1(DS1)|CMOS|LDCC|44PIN|PLASTIC |

| LXT313 | 制造商:LVL1 制造商全稱:LVL1 功能描述:Low Power E1 PCM Repeaters/Transceivers |

| LXT313JE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM Repeater |

| LXT313NE | 制造商:Level One 功能描述:PCM REPEATER, CEPT PCM-30/E-1, 16 Pin, Plastic, DIP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。