- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369873 > LV4124W PDF資料下載

參數(shù)資料

| 型號: | LV4124W |

| 文件頁數(shù): | 7/21頁 |

| 文件大?。?/td> | 277K |

| 代理商: | LV4124W |

No.6000-7/21

LV4124W

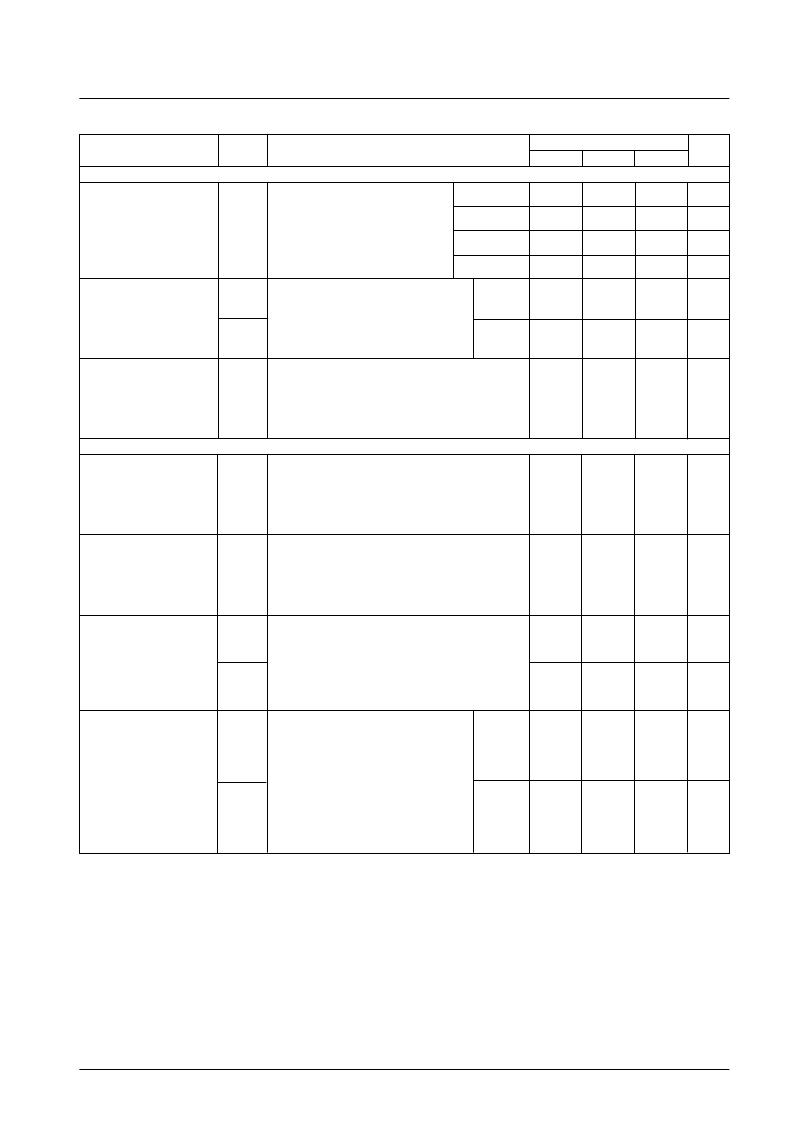

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

[Filter Characteristics]

NTSC 1.50 MHz

–15

–10

dB

Bandpass filter attenuation

ATBPF

PAL

2.00 MHZ

–15

–10

dB

NTSC 5.50 MHz

–7

–2

dB

PAL

6.80 MHz

–8

–3

dB

ATRAPN

NTSC

–40

–30

dB

Trap attenuation

ATRAPP

PAL

–40

–30

dB

R-Y and B-Y low-pass filter

DEMLPF

0.7

0.9

1.1

MHz

[Sync Separator Circuit and TG System]

Input synchronizing signal

amplitude sensitivity

WSSEP

2.0

μs

Sync separator circuit input

sensitivity

VSSEP

40

60

mV

TDSYL

430

630

830

ns

Sync separator circuit output

delay

TDSYH

4.7

5.0

5.3

μs

HPLLN

NTSC

±500

Hz

Horizontal pull-in range

HPLLP

PAL

±500

Hz

Continued on next page.

Input SIG5 (VL = 0 mV) to (A) and SIG1

(0 dB) to (B). Take the T53 chrominance

amplitude when the center frequency

(3.58 and 4.43 MHz) is input to be 0 dB,

and measure the T53 output attenuation

for the frequencies listed at the right.

Input SIG7 (0 dB, 3.58 and 4.43 MHz) to (A)

and measure the T44 output with a spectrum

analyzer. Taking the T44 amplitude in Y/C

mode to be 0 dB, determine the attenuation in

composite input mode.

Input SIG5 (VL = 150 mV) to (A) and SIG2 (0 dB, 3.58 MHz

+ 100 kHz) to (B). Take the T44 output 100 kHz component

am plitude at this time to be 0 dB, and determine the

frequency at which the output beat component is reduced by

3 dB when the SIG2 frequency is increased from 3.58 MHz.

Input SIG5 (VL = 0 mV, VS = 143 mV, variable WS) to (A)

and verify synchronization with the T23 HD output.

Determine the value of WS at the point synchronization with

the T23 HD output is lost when the SIG5 WS is gradually

made narrower starting at 4.7 μs.

Input SIG5 (VL = 0 mV, WS = 4.7 μs, variable VS) to (A) and

verify synchronization with the T23 HD output. Determine the

value of VS at the point synchronization with the T23 HD

output is lost when the SIG5 VS is gradually reduced starting

at 143 mV.

Input SIG5 (VL = 0 mV, WS = 4.7 μs, VS = 143 mV) to (A)

and measure the delay time with respect to the T12 RPD

output. Here, TDSYL is the delay from the fall of the input

HSYNC signal to the fall of the T12 RPD output, and TDSYH

is the delay from the rise of the input HSYNC signal to the

rise of the T12 RPD output.

Input SIG5 (VL = 0 mV, WS = 4.7 μs, VS =

143 mV, variable horizontal frequency) to (A)

and verify synchronization withthe T23 HD

output. Determine the frequency fH at which

synchronization is achieved when the SIG5

horizontal frequency is varied starting from the

state where I/O synchronization is lost.

Calculate HPLLN = fH – 15734 and HPLLP =

fH – 15625.

AC Characteristics (4)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LV4126W | |

| LV560MCRO | Analog IC |

| LV560PLID | Analog IC |

| LV737212M | |

| LV8571A | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LV4126W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LV4135W-MPB-E | 制造商:ON Semiconductor 功能描述:FTRAY / LCD DRIVER ICS |

| LV4137W-MPB-E | 功能描述:LCD 驅(qū)動器 RoHS:否 制造商:Maxim Integrated 數(shù)位數(shù)量:4.5 片段數(shù)量:30 最大時鐘頻率:19 KHz 工作電源電壓:3 V to 3.6 V 最大工作溫度:+ 85 C 最小工作溫度:- 20 C 封裝 / 箱體:PDIP-40 封裝:Tube |

| LV4138W | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Bi-CMOS LSI For LCD Panel Drive Single Chip IC |

| LV4141W | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Bi-CMOS LSI For LCD Panel Drive Single Chip IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。