- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30770 > LTC3615EUF#PBF (LINEAR TECHNOLOGY CORP) SWITCHING REGULATOR, PQCC24 PDF資料下載

參數(shù)資料

| 型號(hào): | LTC3615EUF#PBF |

| 廠商: | LINEAR TECHNOLOGY CORP |

| 元件分類: | 穩(wěn)壓器 |

| 英文描述: | SWITCHING REGULATOR, PQCC24 |

| 封裝: | 4 X 4 MM, LEAD FREE, PLASTIC, MO-220WGGD, QFN-24 |

| 文件頁數(shù): | 27/32頁 |

| 文件大小: | 585K |

| 代理商: | LTC3615EUF#PBF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁

LTC3615/LTC3615-1

4

3615fa

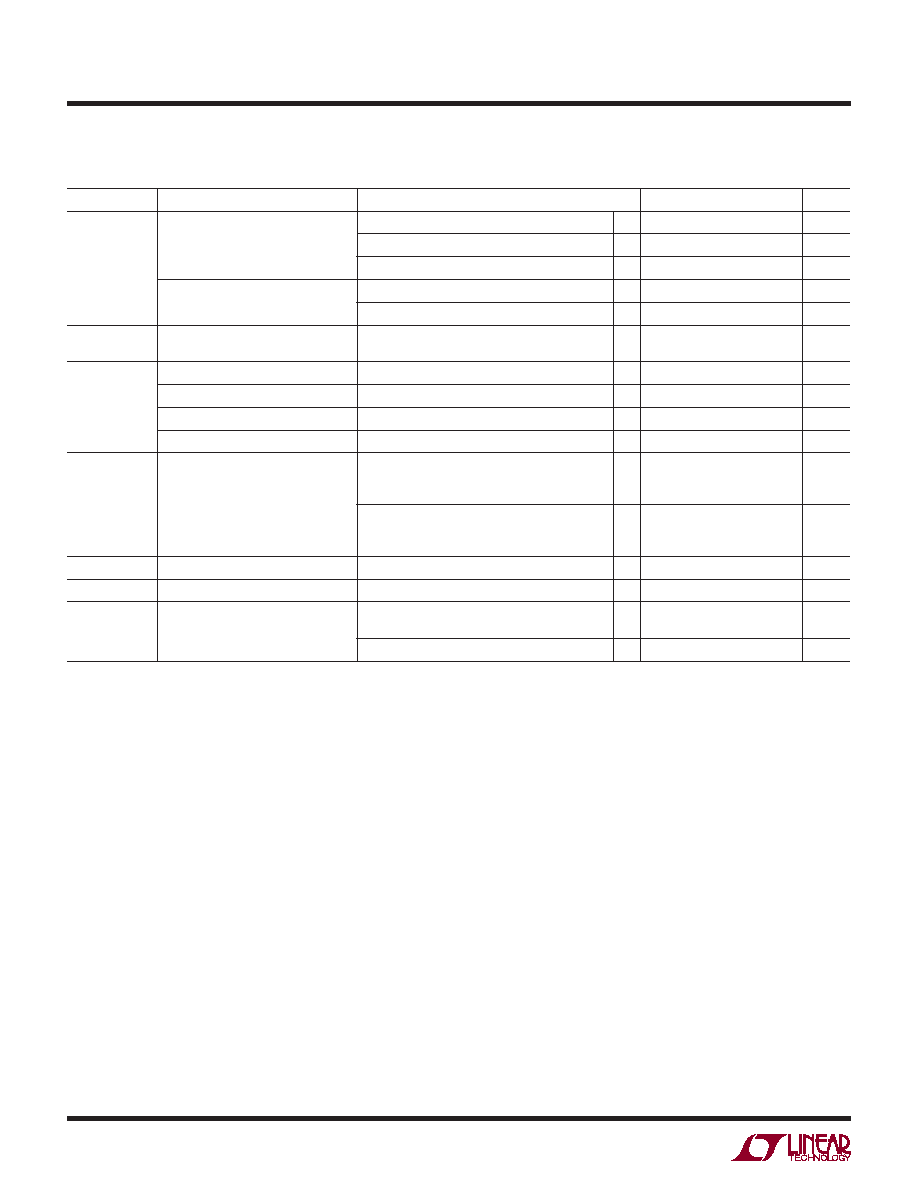

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

SW1–SW2

Output Phase Shift Between SW1

and SW2 (LTC3615)

VPHASE < 0.15 SVIN

0Deg

0.35 SVIN < VPHASE < 0.65 SVIN

90

Deg

VPHASE > 0.85 SVIN

180

Deg

Output Phase Shift Between SW1

and SW2 (LTC3615-1)

VPHASE < 0.65 SVIN

140

Deg

VPHASE > 0.85 SVIN

180

Deg

VSRLIM

Voltage at SRLIM to Enable DDR

Mode

(Note 9)

SVIN – 0.3

V

VMODE

(Note 9)

Internal Burst Mode Operation

0.3

V

Pulse-Skipping Mode

SVIN – 0.3

V

Forced Continuous Mode

1.1

SVIN 0.58

V

External Burst Mode Operation

0.5

0.85

V

PGOOD

Power Good Voltage Windows

TRACK/SSx = SVIN, Entering Window

VFBx Ramping Up

VFBx Ramping Down

–3.5

3.5

–6

6

%

TRACK/SSx = SVIN, Leaving Window

VFBx Ramping Up

VFBx Ramping Down

9

–9

11

–11

%

tPGOOD

Power Good Blanking Time

Entering/Leaving Window

70

105

140

μs

RPGOOD

Power Good Pull-Down On-Resistance I = 10mA

8

12

30

Ω

VRUN

Enable Pin

Input High

Input Low

l

1

0.4

V

Pull-Down Resistance

4

MΩ

ELECTRICAL CHARACTERISTICS

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: The LTC3615/LTC3615-1 are tested under pulsed load conditions

such that TJ ≈ TA. The LTC3615E/LTC3615E-1 are guaranteed to meet

performance specications over the 0°C to 85°C operating junction

temperature range. Specications over the –40°C to 125°C operating

junction temperature range are assured by design, characterization and

correlation with statistical process controls. The LTC3615I/LTC3615I-1 are

guaranteed to meet specications over the full –40°C to 125°C operating

junction temperature range. Note that the maximum ambient temperature

is determined by specic operating conditions in conjunction with board

layout, the rated package thermal resistance and other environmental

factors. Note that the maximum ambient temperature consistent with

these specications is determined by specic operating conditions in

conjunction with board layout, the rated package thermal impedance

and other environmental factors. The junction temperature (TJ, in °C) is

calculated from the ambient temperature

(TA, in °C) and power dissipation (PD, in watts) according to the formula:

TJ = TA + (PD θJA)

where θJA (in °C/W) is the package thermal impedence.

Note 3: This parameter is tested in a feedback loop which servos VFB1,2 to

the midpoint for the error amplier (VITH1,2 = 0.75V).

Note 4: External compensation on ITH pin.

Note 5: Tying the ITH pin to SVIN enables internal compensation and AVP

mode for the selected channel.

Note 6: Dynamic supply current is higher due to the internal gate charge

being delivered at the switching frequency.

Note 7: See description of the TRACK/SS pin in the Pin Functions section.

Note 8: When sourcing current, the average output current is dened

as owing out of the SW pin. When sinking current, the average output

current is dened as owing into the SW pin. Sinking mode requires the

use of forced continuous mode.

Note 9: See description of the MODE pin in the Pin Functions section.

Note 10: Guaranteed by design and correlation to wafer level

measurements for QFN packages.

Note 11: This IC includes overtemperature protection that is intended

to protect the device during momentary overload conditions. Junction

temperature will exceed 125°C when overtemperature protection is active.

Continuous operation above the specied maximum operating junction

temperature may impair device reliability or permanently damage the

device.

The

l denotes the specications which apply over the full operating

junction temperature range, otherwise specications are at TA = 25°C (Note 2), SVIN = PVINx = 3.3V, RT = 178k, RSRLIM = 40.2k, unless

otherwise specied (Note 2).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LTC3615EFE#PBF | SWITCHING REGULATOR, PDSO24 |

| LTC3615IFE-1#PBF | SWITCHING REGULATOR, PDSO24 |

| LTC3615EUF#TRPBF | SWITCHING REGULATOR, PQCC24 |

| LTC3615IFE#PBF | SWITCHING REGULATOR, PDSO24 |

| LTC3727IG-1#TR | 3 A SWITCHING CONTROLLER, 580 kHz SWITCHING FREQ-MAX, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LTC3615HFE#PBF | 制造商:Linear Technology 功能描述:IC REG BUCK SYNC ADJ 3A 24TSSOP |

| LTC3615HFE#TRPBF | 制造商:Linear Technology 功能描述:IC REG BUCK SYNC ADJ 3A 24TSSOP |

| LTC3615HFE-1#PBF | 制造商:Linear Technology 功能描述:IC REG BUCK SYNC ADJ 3A 24TSSOP |

| LTC3615HFE-1#TRPBF | 制造商:Linear Technology 功能描述:IC REG BUCK SYNC ADJ 3A 24TSSOP |

| LTC3615HUF#PBF | 制造商:Linear Technology 功能描述:IC REG BUCK SYNC ADJ 3A 24TSSOP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。