- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369841 > LSI53C140 LSI53C140 Ultra2 SCSI Bus Expander technical manual v2.1 9/01 PDF資料下載

參數(shù)資料

| 型號(hào): | LSI53C140 |

| 英文描述: | LSI53C140 Ultra2 SCSI Bus Expander technical manual v2.1 9/01 |

| 中文描述: | LSI53C140 Ultra2 SCSI總線擴(kuò)展器技術(shù)手冊(cè)2.1 9 / 01 |

| 文件頁(yè)數(shù): | 98/166頁(yè) |

| 文件大?。?/td> | 1330K |

| 代理商: | LSI53C140 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)當(dāng)前第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)

3-50

SAF-TE Source Code

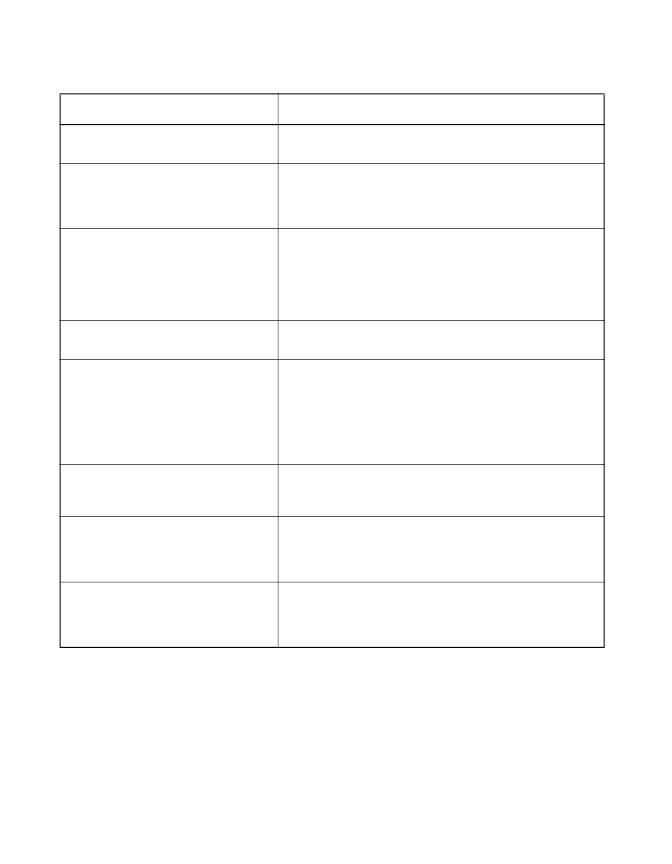

How do we change the flags used

during compilation

Currently, the source code #Define statements must be

modified.

How are SCSI errors reported

Errors during a SCSI transfer or with a CDB are reported

by setting the appropriate check condition. Refer to Section

2.1.3 in the

LSI53C040 Enclosure Services Processor

SAF-TE Firmware User's Guide

for more information.

How are TWS errors reported

Invalid entries in

config

data structure, code load status

variable cl_status are set to CLS_FAILURE_XXX. The XXX

describes the failure and thus check conditions are set. The

initiator may retrieve information by issuing a Mode 4 Write

Buffer command with CDB[3] = 0xFF followed by a Request

Sense command.

Is Timer 2 utilized

Yes. Timer 2 is used to clock the transmission and

reception of data on the serial bus.

What is the difference between a soft

reset and a hard reset

A hard reset is a power on reset. The chip, all registers,

and external data memory are initialized using the contents

of the serial EEPROM. A soft reset occurs when the

watchdog timer expires. This forces only a chip reset. Note

the code restarts but not all of the registers are initialized.

See Chapter 2 in the

LSI53C040 Enclosure Services

Processor Technical Manual

for more information.

What is a shadow register and how is

it used

It holds a duplicate of a register value in xdata data

memory. Use of shadow registers allows for faster access

in some cases.

Prior to transferring the data sent by a

Mode 4 Write Buffer command over

the TWS bus, the byte count variable is

decremented by 1. Why

All Mode 4 Write Buffer commands require that the last

data byte transferred be the checksum of all previous data

bytes. However, this checksum is

not

data to be saved in

the serial EEPROM.

If the firmware is, say 10 Kbytes, but

our SCSI data buffer is only 1025

Bytes, how is the firmware updated

The Initiator, or an application program, must break the

firmware into segments and write one segment at a time.

See the discussion on

Section 3.4.2.3, “Firmware Update,”

page 3-33

for more information.

Table 3.18

Source Code Issues (Cont.)

Question

Comment

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LSI53C141 | LSI53C141 SCSI Bus Expander technical manual v2.1 11/00 |

| LSI53C1510 | LSI53C1510 I2O-Ready PCI RAID Ultra2 SCSI Controller technical manual v2.2 4/01 |

| LSI53C180 | LSI53C180 Ultra160 SCSI Bus Expander technical manual v1.3 6/01 |

| LSI53C770 | LSI53C770 Ultra SCSI I/O Processor technical manual v2.1 3/01 |

| LSI53C810A | LSI53C810A PCI to SCSI I/O Processor technical manual v2.1 3/01 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LSI53C140-160QFP | 制造商:LSI Corporation 功能描述: |

| LSI53C141 | 制造商:LSI Corporation 功能描述: |

| LSI53C1510 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LSI53C1510 I2O-Ready PCI RAID Ultra2 SCSI Controller technical manual v2.2 4/01 |

| LSI53C180 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LSI53C180 Ultra160 SCSI Bus Expander technical manual v1.3 6/01 |

| LSI53C180C1 | 制造商:LSI 功能描述: 制造商:LSI Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。