- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377657 > lpm-counter (Altera Corporation) Parameteruzed Absolute Value(參數(shù)確定的計(jì)數(shù)器) PDF資料下載

參數(shù)資料

| 型號(hào): | lpm-counter |

| 廠商: | Altera Corporation |

| 英文描述: | Parameteruzed Absolute Value(參數(shù)確定的計(jì)數(shù)器) |

| 中文描述: | Parameteruzed絕對值(參數(shù)確定的計(jì)數(shù)器) |

| 文件頁數(shù): | 31/48頁 |

| 文件大小: | 293K |

| 代理商: | LPM-COUNTER |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

26

Altera Corporation

Storage Functions

lpm_ff

Parameterized D or T Flipflop

Ports

Name

Type

Required

Description

aload

Input

No

Asynchronous load input. Asynchronously loads the flipflop with the value on

the

data[]

input. Default = 0. If

aload

is used,

data[]

must be used.

Synchronous set input. Sets the

q[]

outputs to the value specified by

LPM_SVALUE

, if that value is present, or sets the

q[]

outputs to all 1s. If both

sset

and

sclr

are used and both are asserted,

sclr

is dominant. The

sset

input affects the output

q[]

values before polarity is applied to the ports.

Synchronous load input. Loads the flipflop with the value on the

data[]

input

on the next active clock edge. Default = 0. If

sload

is used,

data[]

must be

used. For load operation,

sload

must be high (1) and

enable

must be high

(1) or unconnected.

T flipflop: toggle enable; D flipflop: data input. This port is

LPM_WIDTH

wide. If

the

data[]

port is not used, at least one of the

aset

,

aclr

,

sset

, or

sclr

ports must be used.

Positive-edge-triggered clock.

Clock enable input. Default = 1.

Synchronous clear input. If both

sset

and

sclr

are used and both are

asserted,

sclr

is dominant. The

sclr

input affects the output

q[]

values

before polarity is applied to the ports.

Asynchronous set input. Sets

q[]

outputs to the value specified by

LPM_AVALUE

, if that value is present, or sets the

q[]

outputs to all 1s.

Asynchronous clear input. If both

aset

and

aclr

are used and both are

asserted,

aclr

is dominant. The

aclr

input affects the output

q[]

values

before polarity is applied to the ports.

Data output from D flipflops. This port is

LPM_WIDTH

wide.

sset

Input

No

sload

Input

No

data[]

Input

No

clock

Input

Input

Input

Yes

No

No

enable

sclr

aset

Input

No

aclr

Input

No

q[]

Output

Yes

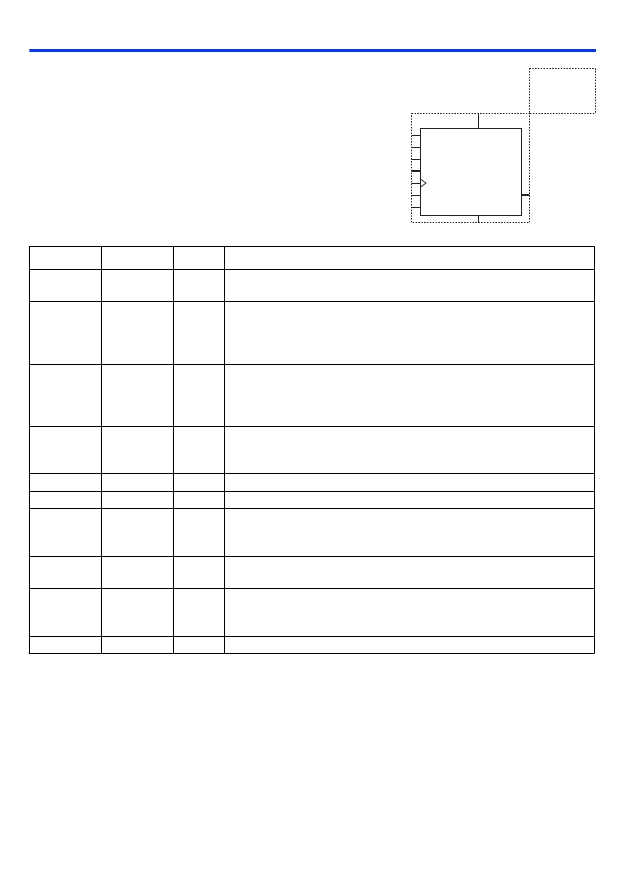

aload

sset

sload

data[]

clock

enable

sclr

LPM_FF

LPM_AVALUE=

LPM_FFTYPE=

LPM_SVALUE=

LPM_WIDTH=

q[]

aclr

aset

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| lpm-compare | Parameteruzed Comparator(參數(shù)確定的比較器) |

| lpm-latch | Parameteruzed Latch(參數(shù)確定的鎖存器) |

| lpm-bustri | Parameterized Tri-State Buffer(參數(shù)確定的三態(tài)緩沖器) |

| lpm-clshift | Parameterized Combinatorial Logic Shifter or Barrel Shifter(參數(shù)確定的組合邏輯移位器或柱式移位器) |

| lpm-shiftreg | Parameteruzed Shift Register(參數(shù)確定的移位寄存器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LPMM-S2 | 制造商:Panduit Corp 功能描述: 制造商: 功能描述: 制造商:undefined 功能描述: |

| LPMM-S2-C | 功能描述:電纜束帶 LOW PROFILE MOUNT RoHS:否 制造商:Phoenix Contact 產(chǎn)品:Cable Tie Mounts 類型:Adhesive 顏色:Black 材料:Acrylonitrile Butadiene Styrene (ABS) 長度:19 mm 寬度:19 mm 抗拉強(qiáng)度: |

| LPMM-S2-M | 功能描述:電纜束帶 Cable Tie Mount, Low Profile, #2 Screw RoHS:否 制造商:Phoenix Contact 產(chǎn)品:Cable Tie Mounts 類型:Adhesive 顏色:Black 材料:Acrylonitrile Butadiene Styrene (ABS) 長度:19 mm 寬度:19 mm 抗拉強(qiáng)度: |

| LPMM-S5 | 制造商:MISCELLANEOUS 功能描述: |

| LPMM-S5-C | 功能描述:電纜束帶 LOW PROFILE MOUNT RoHS:否 制造商:Phoenix Contact 產(chǎn)品:Cable Tie Mounts 類型:Adhesive 顏色:Black 材料:Acrylonitrile Butadiene Styrene (ABS) 長度:19 mm 寬度:19 mm 抗拉強(qiáng)度: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。