- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385498 > LPC3240FET296 (NXP SEMICONDUCTORS) ARM926EJ-S with 256 kB SRAM, USB High-speed OTG, SD-MMC, NAND flash controller, Ethernet PDF資料下載

參數(shù)資料

| 型號(hào): | LPC3240FET296 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | ARM926EJ-S with 256 kB SRAM, USB High-speed OTG, SD-MMC, NAND flash controller, Ethernet |

| 中文描述: | 32-BIT, FLASH, 266 MHz, RISC MICROCONTROLLER, PBGA296 |

| 封裝: | 15 X 15 MM, 0.70 MM PITCH, PLASTIC, MO-216, SOT1048-1, TFBGA-296 |

| 文件頁(yè)數(shù): | 6/17頁(yè) |

| 文件大小: | 121K |

| 代理商: | LPC3240FET296 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

ES_LPC3240

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2011. All rights reserved.

Errata sheet

Rev. 9 — 1 June 2011

6 of 17

NXP Semiconductors

ES_LPC3240

Errata sheet LPC3240

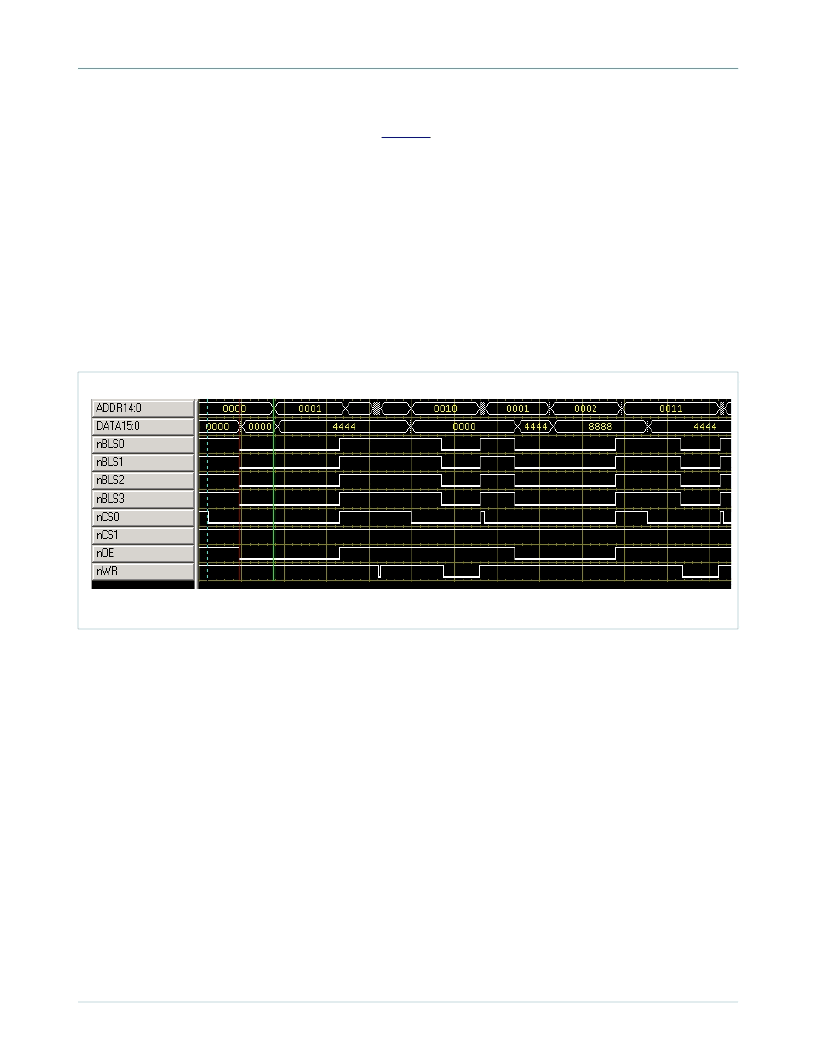

DMA register values used in

Figure 2

:

DMACConfig = 0x01

DMACCxSrcAddr = 0xe0000000; EMC_CS0

DMACCxDestAddr = 0xe0000040; EMC_CS0

DMACCxLLI = 0x0

DMACCxControl = 0x0c480004; Dest & Src addrs increment, Dest & Src 32-bit; Dburst

& Sburst size 1; transfer size 4

DMACCxConfig = 0x01

EMCStaticConfig0 = 0x00000082; 32-bit width, Byte lane state 1

Results of this behavior:

1. DMA reads from an external memory will have lower performance than a software

read loop. The source read burst of two, to get one transfer, will significantly increase

the time to complete all transfers in the memory-to-memory DMA, therefore

decreasing the overall throughput possible on the EMC_CSx_N static memory

interface.

2. Potential unintended consequence when the last DMA read accesses the address

beyond the DMA source buffer address in the FPGA or external peripheral chip. This

extra address is the second access during the last DMA source read.

Fig 2.

Scope shot 2 - actual read timing

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LPV531 | Programmable Micropower CMOS Input, Rail-to-Rail Output Operational Amplifier |

| LPV531MK | Programmable Micropower CMOS Input, Rail-to-Rail Output Operational Amplifier |

| LPV531MKX | Programmable Micropower CMOS Input, Rail-to-Rail Output Operational Amplifier |

| LQA48B | Cellular Phone Power Management Unit |

| LQB08A | Single-Ended Input Motor Driver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LPC3240FET296,551 | 功能描述:ARM微控制器 - MCU ARM9 256KRAM VFP USB OTG ETH RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 處理器系列:STM32F373xx 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:72 MHz 程序存儲(chǔ)器大小:256 KB 數(shù)據(jù) RAM 大小:32 KB 片上 ADC:Yes 工作電源電壓:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:LQFP-48 安裝風(fēng)格:SMD/SMT |

| LPC3240FET296/01 | 制造商:NXP Semiconductors 功能描述:MCU, 16BIT/32BIT, 266MHZ, TFBGA-296 制造商:NXP Semiconductors 功能描述:MCU, 16BIT/32BIT, 266MHZ, TFBGA-296, Controller Family/Series:LPC3200, Core Size 制造商:NXP Semiconductors 功能描述:MCU, 16BIT/32BIT, 266MHZ, TFBGA-296, Controller Family/Series:LPC3200, Core Size:16bit / 32bit, No. of I/O's:87, Supply Voltage Min:2.7V, Supply Voltage Max:3.6V, Digital IC Case Style:TFBGA, No. of Pins:296, Program Memory Size:-, |

| LPC3240FET296/01,5 | 功能描述:ARM微控制器 - MCU ARM9 VFP USB OTG Improved LCD RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 處理器系列:STM32F373xx 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:72 MHz 程序存儲(chǔ)器大小:256 KB 數(shù)據(jù) RAM 大小:32 KB 片上 ADC:Yes 工作電源電壓:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:LQFP-48 安裝風(fēng)格:SMD/SMT |

| LPC3240FET296/01,551 | 制造商:NXP Semiconductors 功能描述:0 |

| LPC3240FET296/015 | 制造商:NXP Semiconductors 功能描述:LPC3240FET296/TFBGA296/TRAYBDP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。