- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358924 > LP3944ISQ (NATIONAL SEMICONDUCTOR CORP) RGB/White/Blue 8-LED Fun Light Driver PDF資料下載

參數(shù)資料

| 型號(hào): | LP3944ISQ |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 顯示驅(qū)動(dòng)器 |

| 英文描述: | RGB/White/Blue 8-LED Fun Light Driver |

| 中文描述: | LED DISPLAY DRIVER, QCC24 |

| 文件頁數(shù): | 6/12頁 |

| 文件大小: | 249K |

| 代理商: | LP3944ISQ |

Application Notes

THEORY OF OPERATION

The LP3944 takes incoming data and feed them into several

registers that control the frequency and the duty cycle of the

LEDs. Two prescaler registers and two PWM registers pro-

vide two individual rates to dim or blink the LEDs (for more

information on these registers, refer to

Table 1. LP3944

REGISTER

TABLE

).

The

microprocessor can program each LED to be in one of four

states—on, off, DIM0 rate or DIM1 rate. One read-only

registers provide status on all 8 LEDs. The LP3944 can be

used to drive RGB LEDs and/or single-color LEDs to create

a colorful, entertaining, and informative setting. This is par-

ticularly suitable for accessory functions in cellular phones

and toys. Any LED pins not used to drive LED can be used

for General Purpose Parallel Input/Output (GPIO) expan-

sion.

baseband

controller/

The LP3944 is equipped with Power-On Reset that holds the

chip in a reset state until V

reaches V

during power up.

Once V

is achieved, the LP3944 comes out of reset and

initializes itself to the default state.

To bring the LP3944 into reset, hold the RST pin LOW for a

period of TW. This will put the chip to its default state. The

LP3944 can only be programmed after RST signal is HIGH

again.

I

2

C DATA VALIDITY

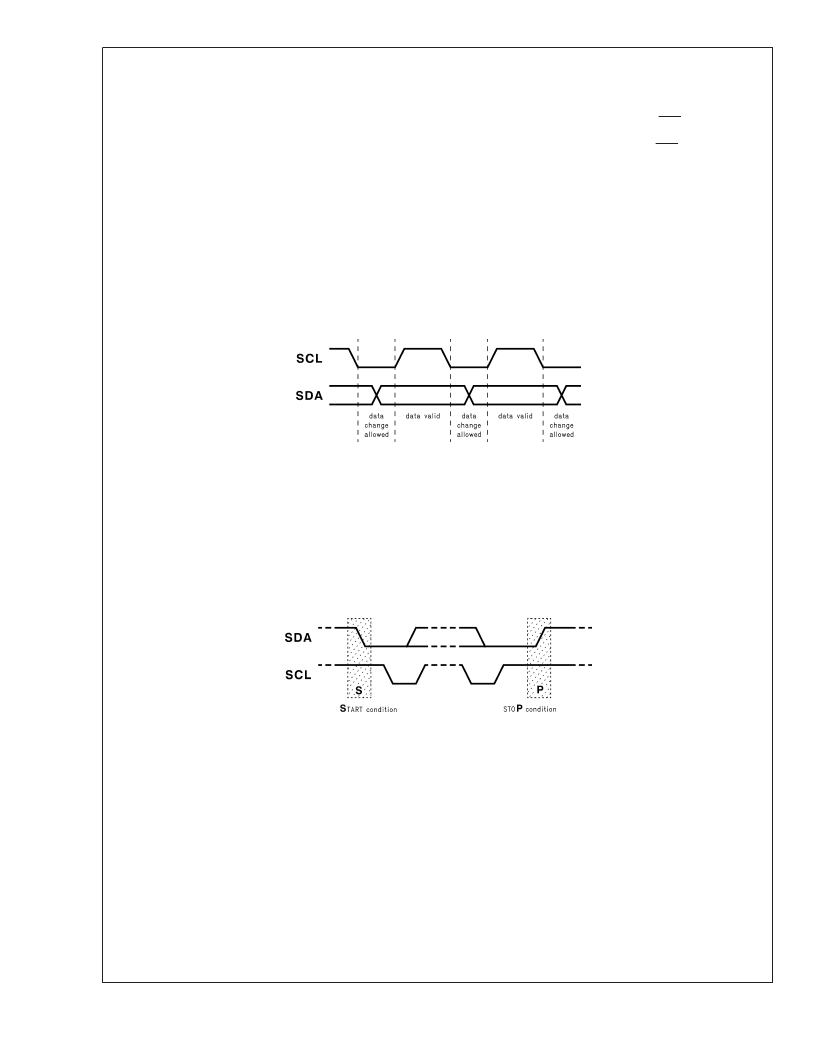

The data on SDA line must be stable during the HIGH period

of the clock signal (SCL). In other words, state of the data

line can only be changed when CLK is LOW.

I

2

C START AND STOP CONDITIONS

START and STOP bits classify the beginning and the end of

the I

2

C session. START condition is defined as SDA signal

transitioning from HIGH to LOW while SCL line is HIGH.

STOP condition is defined as the SDA transitioning from

LOW to HIGH while SCL is HIGH. The I

2

C master always

generates START and STOP bits. The I

2

C bus is considered

to be busy after START condition and free after STOP con-

dition. During data transmission, I

2

C master can generate

repeated START conditions. First START and repeated

START conditions are equivalent, function-wise.

TRANSFERRING DATA

Every byte put on the SDA line must be eight bits long with

the most significant bit (MSB) being transferred first. The

number of bytes that can be transmitted per transfer is

unrestricted. Each byte of data has to be followed by an

acknowledge bit. The acknowledge related clock pulse is

generated by the master. The transmitter releases the SDA

line (HIGH) during the acknowledge clock pulse. The re-

ceiver must pull down the SDA line during the 9th clock

pulse, signifying an acknowledge.Areceiver which has been

addressed must generate an acknowledge after each byte

has been received.

After the START condition, a chip address is sent by the I

2

C

master. This address is seven bits long followed by an eighth

bit which is a data direction bit (R/W). The LP3944 hardwires

bits 7 to 4 and leaves bits 3 to 1 selectable, as shown in

Figure 3

. For the eighth bit, a “0” indicates a WRITE and a

“1” indicates a READ. The LP3944 supports only a WRITE

during chip addressing. The second byte selects the register

to which the data will be written. The third byte contains data

to write to the selected register.

20085306

FIGURE 1. I

2

C Data Validity

20085307

FIGURE 2. I

2

C START and STOP Conditions

L

www.national.com

6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LP3944ISQX | RGB/White/Blue 8-LED Fun Light Driver |

| LP3944 | RGB/White/Blue 8-LED Fun Light Driver |

| LP3945 | Battery Charge Management System |

| LP3945ILD | Battery Charge Management System |

| LP3945ILDX | Battery Charge Management System |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LP3944ISQ/NOPB | 功能描述:LED照明驅(qū)動(dòng)器 RoHS:否 制造商:STMicroelectronics 輸入電壓:11.5 V to 23 V 工作頻率: 最大電源電流:1.7 mA 輸出電流: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SO-16N |

| LP3944ISQEV | 功能描述:電源管理IC開發(fā)工具 LP3944 EVAL BOARD RoHS:否 制造商:Maxim Integrated 產(chǎn)品:Evaluation Kits 類型:Battery Management 工具用于評(píng)估:MAX17710GB 輸入電壓: 輸出電壓:1.8 V |

| LP3944ISQEV/NOPB | 制造商:Texas Instruments 功能描述:Evaluation Board For LED Driver 8Segment 2.5V/3.3V/5V T/R |

| LP3944ISQX | 功能描述:LED照明驅(qū)動(dòng)器 RoHS:否 制造商:STMicroelectronics 輸入電壓:11.5 V to 23 V 工作頻率: 最大電源電流:1.7 mA 輸出電流: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SO-16N |

| LP3944ISQX/NOPB | 功能描述:LED照明驅(qū)動(dòng)器 RoHS:否 制造商:STMicroelectronics 輸入電壓:11.5 V to 23 V 工作頻率: 最大電源電流:1.7 mA 輸出電流: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SO-16N |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。