- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358877 > LM96000 (National Semiconductor Corporation) Hardware Monitor with Integrated Fan Control PDF資料下載

參數(shù)資料

| 型號: | LM96000 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | Hardware Monitor with Integrated Fan Control |

| 中文描述: | 硬件監(jiān)控集成風扇控制 |

| 文件頁數(shù): | 25/28頁 |

| 文件大小: | 695K |

| 代理商: | LM96000 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁

Functional Description

(Continued)

– The fan will remain on, at Fan PWM Minimum, until the temperature goes a certain amount below Fan Temp Limit.

– The Hysteresis registers control this amount. See below table for details.

These registers become Read Only when the Ready/Lock/Start/Override register Lock bit is set. Any further attempts to write to

thses registers shall have no effect. After power up the default value is used whenever the Ready/Lock/Start/Override register

Start bit is cleared even though modifications to this register are possible.

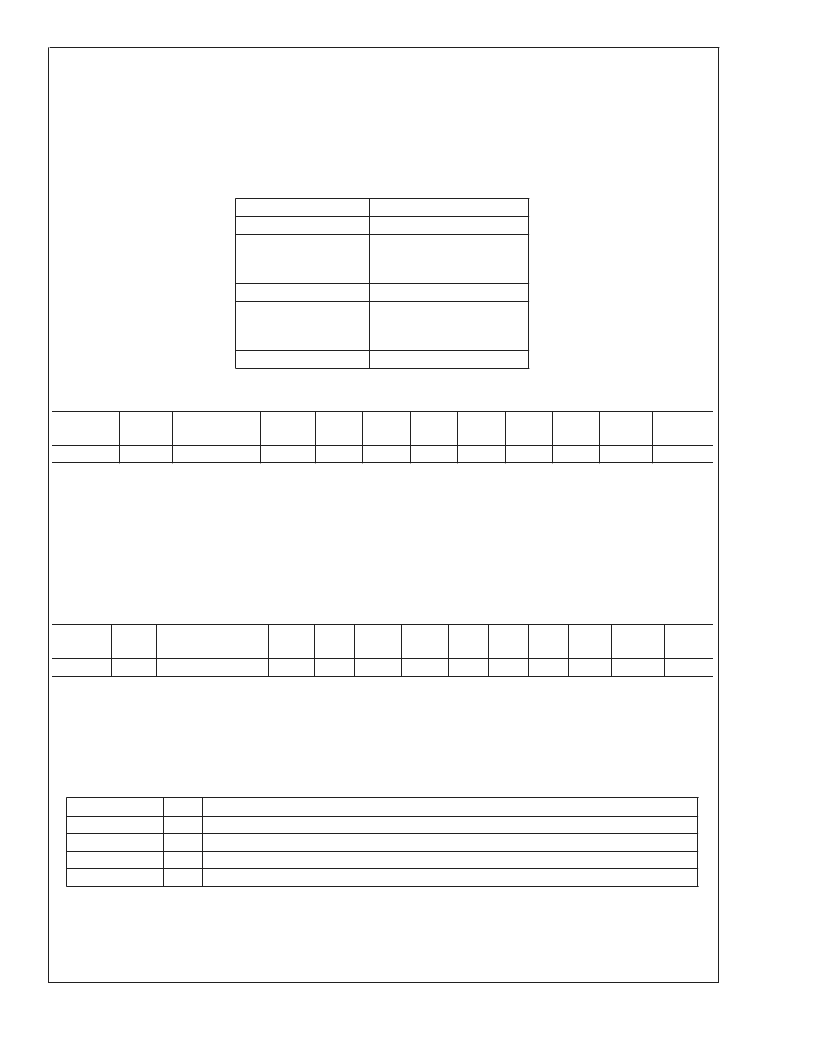

TABLE 12. Hysteresis Settings

Setting

0h

.

.

.

5h

.

.

.

Fh

HYSTERESIS

0C

.

.

.

5C

.

.

.

15C

4.21 Register 6Fh: Test Register

Register

Address

6Fh

Read/

Write

R/W

Register

Name

Test Register

Bit 7

(MSB)

RES

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

(LSB)

XEN

Default

Value

00h

RES

RES

RES

RES

RES

RES

If the XEN bit is set high, the part will be placed into XOR tree test mode. Clearing the bit (writing a 0 to the XEN bit) brings the

part out of XOR tree test mode.

This register becomes Read Only when the Ready/Lock/Start/Override register Lock bit is set.Any further attempts to write to this

registers shall have no effect. After power up the default value is used whenever the Ready/Lock/Start/Override register Start bit

is cleared even though modifications to this register are possible.

4.22 Registers 70-7Fh: Vendor Specific Registers

These registers are for vendor specific features, including test registers. They will not default to a specific value on power up.

4.22.1 Register 74h: Tachometer Monitor Mode

Register

Address

74h

Read/

Write

R/W

Register

Name

Bit 7

(MSb)

RES

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

(LSb)

T1-0

Default

Value

00h

Lock

Tach Monitor Mode

RES

T3/4-1

T3/4-0

T2-1

T2-0

T1-1

Each fan TACH input has 4 possible modes of operation when using the low frequency range for the PWM outputs. Mode 0 is the

only mode that is available when using the high frequecy range for the PWM outputs. The modes for TACH3 and TACH4 share

control bits T3/4-[1:0]; TACH2 is controlled by T2-[1:0]; TACH1 is controlled by T1-[1:0]. The result reported in all modes is based

on 2 pulses per revolution. In order for modes 2 and 3 to function properly it is required that the:

PWM1 output must control the fan that has it’s tachometer output connected to the TACH1 LM96000 input.

PWM2 output must control the fan that has it’s tachometer output connected to the TACH2 LM96000 input.

PWM3 output must control the fans that have their tachometer outputs connected to the TACH3 or TACH4 LM96000 inputs.

Setting (Tn[1:0]) Mode Function

00

01

10

11

0

1

2

3

Traditional tach input monitor, false readings when under minimum detctable RPM

Traditional tach input monitor, FFFFh reading when under minimum detectable RPM

Most accurate readings, FFFFh reading when under minimum detectable RPM

Least effect on programmed PWM of Fan, FFFFh reading when under minimum detectable RPM

Mode 0:

This mode uses the conventional method for fan tachometer pulse detection and does not include any circuitry to

compensate for PWM Fan drive. This mode should be used when PWM drive is not used to power the fan. This mode may

report a false RPM reading when under minimum detectable RPM as shown in the following table.

Mode 1:

This mode uses the conventional method for fan tach detection. The reading will be FFFFh if it is below minimum

detectable RPM.

L

www.national.com

25

相關PDF資料 |

PDF描述 |

|---|---|

| LM96000CIMT | Hardware Monitor with Integrated Fan Control |

| LM96000CIMTX | Hardware Monitor with Integrated Fan Control |

| LM9617CCEA | Monochrome CMOS Image Sensor VGA 30 FPS |

| LM9617 | Monochrome CMOS Image Sensor VGA 30 FPS |

| LM9628EVAL-KIT | LM9628 Color CMOS Image Sensor VGA 30 FPS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LM96000CIMT | 功能描述:板上安裝溫度傳感器 RoHS:否 制造商:Omron Electronics 輸出類型:Digital 配置: 準確性:+/- 1.5 C, +/- 3 C 溫度閾值: 數(shù)字輸出 - 總線接口:2-Wire, I2C, SMBus 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 最大工作溫度:+ 50 C 最小工作溫度:0 C 關閉: 安裝風格: 封裝 / 箱體: 設備功能:Temperature and Humidity Sensor |

| LM96000CIMT/NOPB | 功能描述:板上安裝溫度傳感器 HW Monitor RoHS:否 制造商:Omron Electronics 輸出類型:Digital 配置: 準確性:+/- 1.5 C, +/- 3 C 溫度閾值: 數(shù)字輸出 - 總線接口:2-Wire, I2C, SMBus 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 最大工作溫度:+ 50 C 最小工作溫度:0 C 關閉: 安裝風格: 封裝 / 箱體: 設備功能:Temperature and Humidity Sensor |

| LM96000CIMT/NOPB | 制造商:Texas Instruments 功能描述:Temperature Sensor IC |

| LM96000CIMTX | 功能描述:板上安裝溫度傳感器 RoHS:否 制造商:Omron Electronics 輸出類型:Digital 配置: 準確性:+/- 1.5 C, +/- 3 C 溫度閾值: 數(shù)字輸出 - 總線接口:2-Wire, I2C, SMBus 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 最大工作溫度:+ 50 C 最小工作溫度:0 C 關閉: 安裝風格: 封裝 / 箱體: 設備功能:Temperature and Humidity Sensor |

| LM96000CIMTX/NOPB | 功能描述:板上安裝溫度傳感器 RoHS:否 制造商:Omron Electronics 輸出類型:Digital 配置: 準確性:+/- 1.5 C, +/- 3 C 溫度閾值: 數(shù)字輸出 - 總線接口:2-Wire, I2C, SMBus 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 最大工作溫度:+ 50 C 最小工作溫度:0 C 關閉: 安裝風格: 封裝 / 箱體: 設備功能:Temperature and Humidity Sensor |

發(fā)布緊急采購,3分鐘左右您將得到回復。