- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361034 > LM78CCVF (NATIONAL SEMICONDUCTOR CORP) Microprocessor System Hardware Monitor PDF資料下載

參數(shù)資料

| 型號: | LM78CCVF |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 模擬信號調(diào)理 |

| 英文描述: | Microprocessor System Hardware Monitor |

| 中文描述: | SPECIALTY ANALOG CIRCUIT, PQFP44 |

| 封裝: | PLASTIC, QFP-44 |

| 文件頁數(shù): | 11/31頁 |

| 文件大?。?/td> | 424K |

| 代理商: | LM78CCVF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

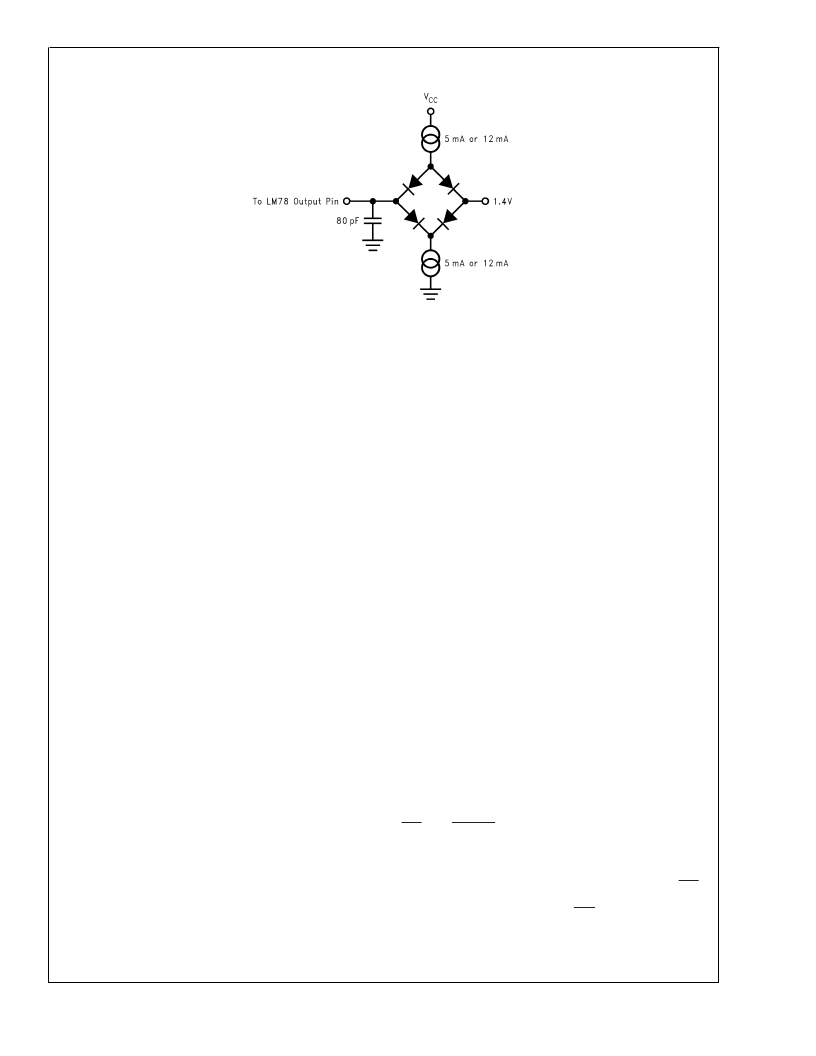

Test Circuit

Functional Description

1.0 GENERAL DESCRIPTION

The LM78 provides 7 analog inputs, a temperature sensor, a

Delta-Sigma ADC (Analog-to-Digital Converter), 3 fan speed

counters, WATCHDOG registers, and a variety of inputs and

outputs on a single chip. Interfaces are provided for both the

ISA parallel bus or Serial Bus. The LM78 performs power

supply, temperature, and fan monitoring for personal com-

puters.

The LM78 continuously converts analog inputs to 8-bit digital

words with a 16 mV LSB (Least Significant Bit) weighting,

yielding input ranges of from 0V to 4.096V. The two negative

analog

inputs

provide

inverting

non-inverting input referred to ground. With additional exter-

nal feedback components, these inputs provide measure-

ments of negative voltages (such as -5V and -12V power

supplies). The analog inputs are useful for monitoring sev-

eral power supplies present in a typical computer. Tempera-

ture is converted to an 8-bit two’s-complement digital word

with a 1C LSB.

Fan inputs measure the period of tachometer pulses from

the fans, providing a higher count for lower fan speeds. The

fan inputs are digital inputs with an acceptable range of 0V to

5V and a transition level of approximately 1.4V. Full scale fan

counts are 255 (8-bit counter) and this represents a stopped

or very slow fan. Nominal speeds, based on a count of 153,

are programmable from 1100 to 8800 RPM on FAN1 and

FAN2, with FAN3 fixed at 4400 RPM. Signal conditioning

circuitry is included to accommodate slow rise and fall times.

The LM78 provides a number of internal registers, as de-

tailed in Figure 6 These include:

Configuration Register:

figuration.

Interrupt Status Registers:

status of each WATCHDOG limit or Interrupt event.

Interrupt Mask Registers:

vidual Interrupt sources, as well as separate masking for

each of both hardware Interrupt outputs.

VID/Fan Divisor Registers:

tus of the VID input lines. The high bits of this register

contain the divisor bits for FAN1 and FAN2 inputs.

op

amps,

with

their

Provides control and con-

Two registers to provide

Allows masking of indi-

A register to read the sta-

Serial Bus Address Register:

address. At power on it assumes the default value of

0101101 binary, and can be altered via the ISA or Serial

Bus interface.

Chip Reset/ID Register:

Allows reseting of all the reg-

isters to the default power-on reset value. Provides a bit

for identification between the current version of this de-

vice and an older version which does not have this reset

capability.

POST RAM:

FIFO RAM to store up to 32 bytes of 8-bit

POST codes. Overflow of the POST RAM will set an

Interrupt. The POST RAM, located at base address x0h

and x4h, allows for easy decoding to address 80h and

84h, the normal addresses for outputting of POST codes.

Interrupt will only be set when writing to port x0h or x4h.

The POST RAM can be read via ports 85h and 86h.

Value RAM:

The monitoring results: temperature, volt-

ages, fan counts, and WATCHDOG limits are all con-

tained in the Value RAM. The Value RAM consists of a

total of 64 bytes. The first 11 bytes are all of the results,

the next 19 bytes are the WATCHDOG limits, and are

located at 20h-3Fh, including two unused bytes in the

upper locations. The next 32 bytes, located at 60h-7Fh,

mirror the first 32 bytes with identical contents. The only

difference in the upper bytes are that they auto-increment

the LM78 Internal Address Register when read from or

written to via the ISA bus (auto-increment is not available

for Serial Bus communications).

When the LM78 is started, it cycles through each measure-

ment in sequence, and it continuously loops through the

sequence approximately once every second. Each mea-

sured value is compared to values stored in WATCHDOG, or

Limit registers. When the measured value violates the pro-

grammed limit the LM78 will set a corresponding Interrupt in

the Interrupt Status Registers. Two hardware Interrupt lines,

SMI and NMI/IRQ, are fully programmable with separate

masking of each Interrupt source, and masking of each

output. In addition, the Configuration Register has control

bits to enable or disable the hardware Interrupts.

Additional digital inputs are provided for chaining of SMI

(System Management Interrupt), outputs of multiple external

LM75 temperature sensors via the BTI (Board Temperature

Interrupt) input, and a Chassis Intrusion input. The Chassis

Intrusion input is designed to accept an active high signal

from an external circuit that latches when the case is re-

moved from the computer.

Contains the Serial Bus

DS012873-8

FIGURE 5. Digital Output Load Circuitry

L

www.national.com

11

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM78CCVF-J | Microprocessor System Hardware Monitor |

| LM79CCVF | Microprocessor System Hardware Monitor |

| LM79 | |

| LM81CIMTX-32 | Serial Interface ACPI-Compatible Microprocessor System |

| LM81 | Serial Interface ACPI-Compatible Microprocessor System |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM78CCVF-J | 制造商:National Semiconductor Corporation 功能描述:Data Acquisition System, 7 Channel, 8 Bit, 44 Pin, Plastic, QFP 制造商:Texas Instruments 功能描述:Data Acquisition System, 7 Channel, 8 Bit, 44 Pin, Plastic, QFP |

| LM78D05A | 制造商:CYSTEKEC 制造商全稱:Cystech Electonics Corp. 功能描述:Three Terminal Positive Voltage Regulators |

| LM78D05AJ3 | 制造商:CYSTEKEC 制造商全稱:Cystech Electonics Corp. 功能描述:Three Terminal Positive Voltage Regulators |

| LM78D05B | 制造商:CYSTEKEC 制造商全稱:Cystech Electonics Corp. 功能描述:Three Terminal Positive Voltage Regulators |

| LM78D05BJ3 | 制造商:CYSTEKEC 制造商全稱:Cystech Electonics Corp. 功能描述:Three Terminal Positive Voltage Regulators |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。