- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369782 > LM1881MX TV/Video Sync Circuit PDF資料下載

參數(shù)資料

| 型號(hào): | LM1881MX |

| 英文描述: | TV/Video Sync Circuit |

| 中文描述: | 電視/視頻同步電路 |

| 文件頁(yè)數(shù): | 2/10頁(yè) |

| 文件大?。?/td> | 172K |

| 代理商: | LM1881MX |

Absolute Maximum Ratings

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage

13.2V

Input Voltage

3 Vpp (V

CC

e

5V)

6 Vpp (V

CC

t

8V)

Output Sink Currents; Pins 1, 3, 5

5 mA

Output Sink Current; Pin 7

2 mA

Package Dissipation (Note 1)

1100 mW

0

§

C

b

70

§

C

Operating Temperature Range

Storage Temperature Range

b

65

§

C to

a

150

§

C

ESD Susceptibility (Note 2)

2 kV

Soldering Information

Dual-In-Line Package (10 sec.)

Small Outline Package

Vapor Phase (60 sec.)

Infrared (15 sec.)

260

§

C

215

§

C

220

§

C

See AN-450 ‘‘Surface Mounting Methods and their Effect on

Product Reliability’’ for other methods of soldering surface

mount devices.

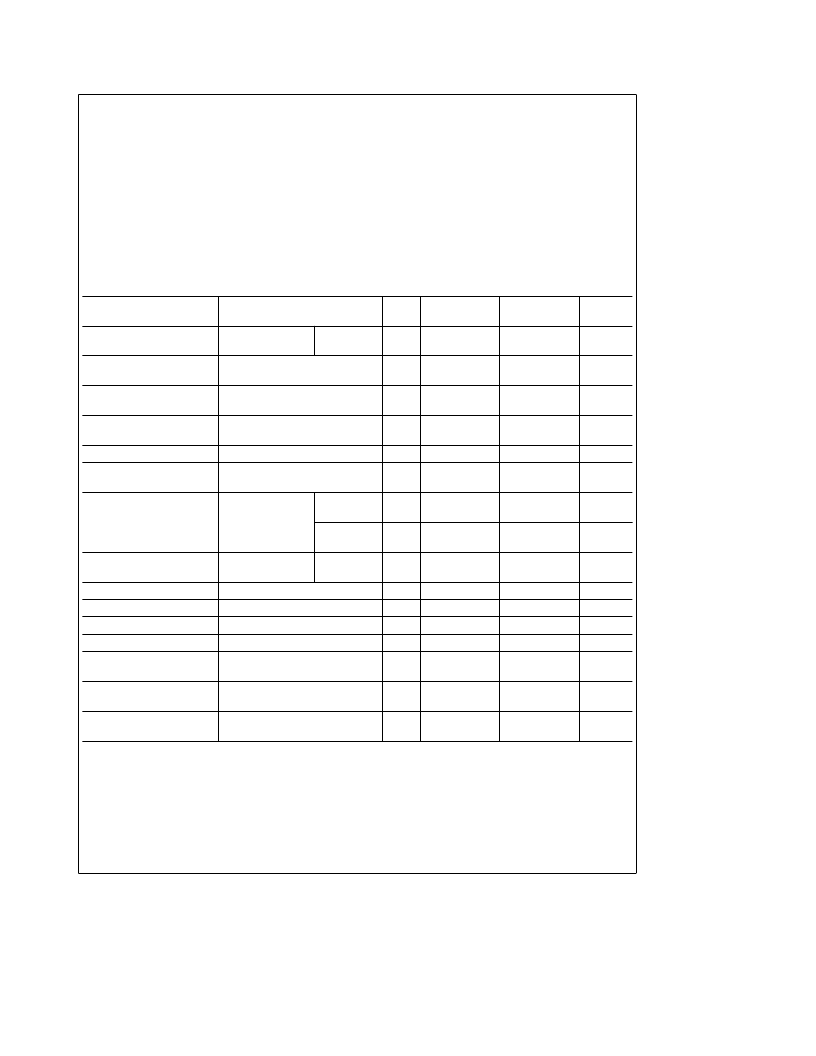

Electrical Characteristics

V

CC

e

5V; Rset

e

680 k

X

; T

A

e

25

§

C; Unless otherwise specified

Parameter

Conditions

Typ

Tested

Limit (Note 3)

Design

Limit (Note 4)

Units

(Limits)

Supply Current

Outputs at Logic 1

V

CC

e

5V

V

CC

e

12V

5.2

5.5

10

12

mAmax

mAmax

DC Input Voltage

Pin 2

1.5

1.3

1.8

Vmin

Vmax

Note 5

70

55

85

mVmin

mVmax

Input Discharge Current

Pin 2; V

IN

e

2V

11

6

m

Amin

m

Amax

16

Input Clamp Charge Current

Pin 2; V

IN

e

1V

0.8

0.2

mAmin

R

SET

Pin Reference Voltage

Pin 6; Note 6

1.22

1.10

1.35

Vmin

Vmax

Composite Sync. & Vertical

Outputs

I

OUT

e

40

m

A;

Logic 1

V

CC

e

5V

V

CC

e

12V

4.5

4.0

11.0

Vmin

Vmin

I

OUT

e

1.6 mA

Logic 1

V

CC

e

5V

V

CC

e

12V

3.6

2.4

10.0

Vmin

Vmin

Burst Gate & Odd/Even

Outputs

I

OUT

e

40

m

A;

Logic 1

V

CC

e

5V

V

CC

e

12V

4.5

4.0

11.0

Vmin

Vmin

Composite Sync. Output

I

OUT

e b

1.6 mA; Logic 0; Pin 1

0.2

0.8

Vmax

Vertical Sync. Output

I

OUT

e b

1.6 mA; Logic 0; Pin 3

0.2

0.8

Vmax

Burst Gate Output

I

OUT

e b

1.6 mA; Logic 0; Pin 5

0.2

0.8

Vmax

Odd/Even Output

I

OUT

e b

1.6 mA; Logic 0; Pin 7

0.2

0.8

Vmax

Vertical Sync Width

230

190

300

m

smin

m

smax

Burst Gate Width

2.7 k

X

from Pin 5 to V

CC

4

2.5

4.7

m

smin

m

smax

Vertical Default Time

Note 7

65

32

90

m

smin

m

smax

Note 1:

For operation in ambient temperatures above 25

§

C, the device must be derated based on a 150

§

C maximum junction temperature and a package thermal

resistance of 110

§

C/W, junction to ambient.

Note 2:

ESD susceptibility test uses the ‘‘human body model, 100 pF discharged through a 1.5 k

X

resistor’’.

Note 3:

Typicals are at T

J

e

25

§

C and represent the most likely parametric norm.

Note 4:

Tested Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 5:

Relative difference between the input clamp voltage and the minimum input voltage which produces a horizontal output pulse.

Note 6:

Careful attention should be made to prevent parasitic capacitance coupling from any output pin (Pins 1, 3, 5, and 7) to the R

SET

pin (Pin 6).

Note 7:

Delay time between the start of vertical sync (at input) and the vertical output pulse.

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM1886N | Color Encoder Circuit |

| LM195K-MIL | BLOWOUT RESISTANT TRANSISTOR|BIPOLAR/JFET|TO-204/-3|3PIN|METAL |

| LM195 | Ultra Reliable Power Transistors |

| LM1971MX | Tone/Volume/Balance Control |

| LM1973MX | Tone/Volume/Balance Control |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM1881M-X | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LM1881 Video Sync Separator |

| LM1881MX/NOPB | 功能描述:視頻 IC VIDEO SYNC SEPARATOR RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| LM1881M-X/NOPB | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| LM1881MX-X/NOPB | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| LM1881N | 功能描述:視頻 IC RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。