- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358798 > LH543601M-30 (Sharp Corporation) 256 x 36 x 2 Bidirectional FIFO PDF資料下載

參數(shù)資料

| 型號(hào): | LH543601M-30 |

| 廠商: | Sharp Corporation |

| 英文描述: | 256 x 36 x 2 Bidirectional FIFO |

| 中文描述: | 256 × 36 × 2雙向先進(jìn)先出 |

| 文件頁(yè)數(shù): | 17/43頁(yè) |

| 文件大小: | 360K |

| 代理商: | LH543601M-30 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)

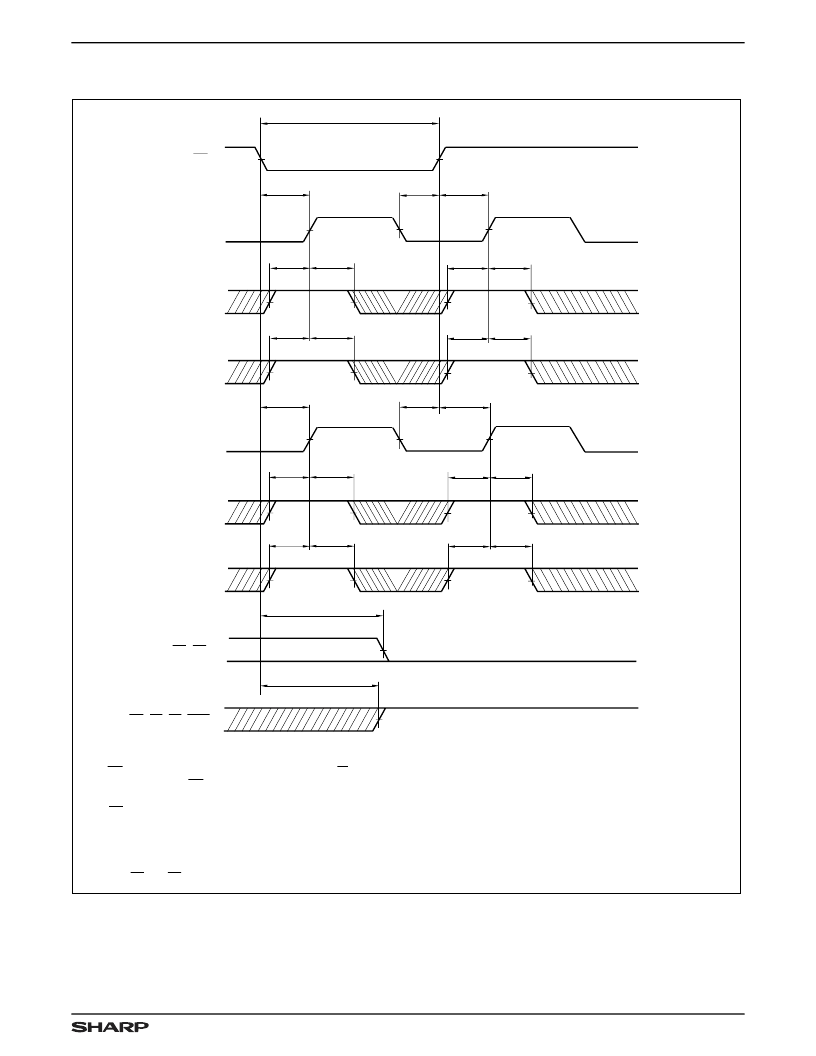

TIMING DIAGRAMS

RS

A

CK

EN

HF, AF, FF, MBF

A

EF, AE

EH

t

ES

t

EH

t

ES

t

RS

t

EH

t

ES

t

EH

t

ES

t

CK

B

EN

B

RSS

t

RSH

t

RSS

t

RSS

t

RSH

t

RSS

t

RF

t

RF

t

NOTES:

1. RS overrides all other input signals, except for R/W

A

, EN

A

, and REQ

A

. It operates

asynchronously. RS operates whether or not EN

A

and/or EN

B

are asserted. However,

at least one rising edge and one falling edge of both CK

A

and CK

B

must occur while

RS is being asserted (is LOW), with timing as defined by t

RSS

and t

RSH

.

2. Otherwise, t

RSS

, t

RSH

need not be met unless the rising edge of CK

A

and/or CK

B

occurs while that clock is enabled.

3. The parity-check even/odd selection (Control Register bit 00) is initialized to odd byte

parity at reset (HIGH).

4. The AE and AF flag offsets are initialized to eight locations from the boundary at reset.

543601-26

REQ

A

t

RQS

t

RQH

REQ

B

t

RQS

t

RQH

t

RQS

t

RQH

t

RQS

t

RQH

Figure 8. Reset Timing

256

×

36

×

2 Bidirectional FIFO

LH543601

17

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LH543601M-35 | 256 x 36 x 2 Bidirectional FIFO |

| LH543601P-20 | 256 x 36 x 2 Bidirectional FIFO |

| LH543601P-25 | 256 x 36 x 2 Bidirectional FIFO |

| LH543601P-30 | 256 x 36 x 2 Bidirectional FIFO |

| LH543601P-35 | 256 x 36 x 2 Bidirectional FIFO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LH543601M-35 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:256 x 36 x 2 Bidirectional FIFO |

| LH543601P-20 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:256 x 36 x 2 Bidirectional FIFO |

| LH543601P-25 | 制造商:Sharp Microelectronics Corporation 功能描述: 制造商:Sharp Microelectronics Corporation 功能描述:512 X 36 BI-DIRECTIONAL FIFO, PQFP132 |

| LH543601P-30 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:256 x 36 x 2 Bidirectional FIFO |

| LH543601P-35 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:256 x 36 x 2 Bidirectional FIFO |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。