- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377631 > LFEC33E-4F672C (LATTICE SEMICONDUCTOR CORP) ECONOLINE: RSZ/P - 1kVDC PDF資料下載

參數(shù)資料

| 型號(hào): | LFEC33E-4F672C |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | FPGA |

| 英文描述: | ECONOLINE: RSZ/P - 1kVDC |

| 中文描述: | FPGA, 4096 CLBS, 32800 GATES, 420 MHz, PBGA672 |

| 封裝: | 27 X 27 MM, FPBGA-672 |

| 文件頁數(shù): | 50/117頁 |

| 文件大小: | 557K |

| 代理商: | LFEC33E-4F672C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁當(dāng)前第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁

3-14

DC and Switching Characteristics

LatticeECP/EC Family Data Sheet

Lattice Semiconductor

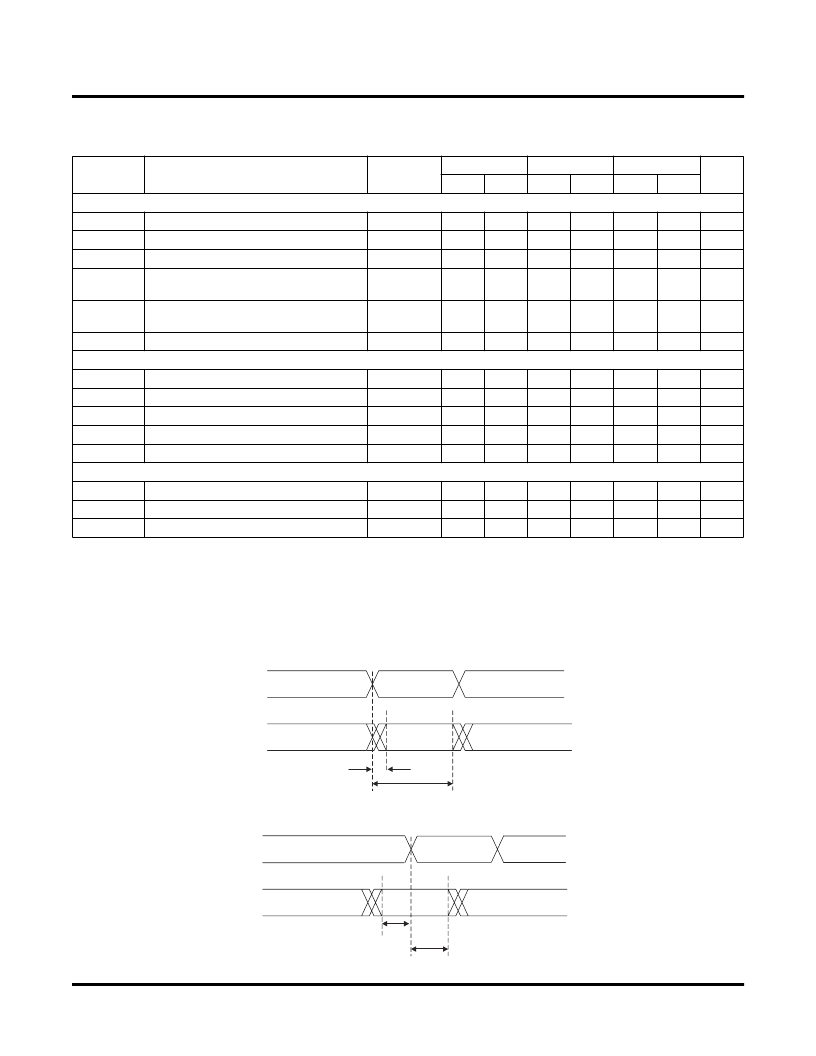

LatticeECP/EC External Switching Characteristics

Over Recommended Operating Conditions

Figure 3-6. DDR Timings

Parameter

General I/O Pin Parameters (Using Primary Clock without PLL)

1

t

CO

Clock to Output - PIO Output Register

t

SU

Clock to Data Setup - PIO Input Register

t

H

Clock to Data Hold - PIO Input Register

Clock to Data Setup - PIO Input Register

with data input delay

Clock to Data Hold - PIO Input Register

with Input Data Delay

f

MAX_IO

LVDS I/O Buffer Frequency

DDR I/O Pin Parameters

2, 3

t

DVADQ

Data Valid After DQS (DDR Read)

t

DVEDQ

Data Hold After DQS (DDR Read)

t

DQVBS

Data Valid Before DQS

t

DQVAS

Data Valid After DQS

f

MAX_DDR

DDR Clock Frequency

Primary and Secondary Clock

f

MAX_PRI

Frequency for Primary Clock Tree

t

W_PRI

Clock Pulse Width for Primary Clock

t

SKEW_PRI

Primary Clock Skew within an I/O Bank

1. General timing numbers based on LVCMOS2.5V, 12 mA.

2. DDR timing numbers based on SSTL I/O.

3. DDR speci

fi

cations are characterized but not tested.

4. UI is average bit period.

Rev F 0.17

Description

Device

-5

-4

-3

Units

Min.

Max.

Min.

Max.

Min.

Max.

LFEC20

LFEC20

LFEC20

—

0.00

3.41

5.71

—

—

—

0.00

4.09

6.85

—

—

—

0.00

4.77

7.99

—

—

ns

ns

ns

t

SU_DEL

LFEC20

3.84

—

4.62

—

5.38

—

ns

t

H_DEL

LFEC20

-0.44

—

-0.54

—

-0.61

—

ns

LFEC20

—

420

—

378

—

340

MHz

4

LFEC20

LFEC20

LFEC20

LFEC20

LFEC20

—

0.192

—

—

—

200

—

0.192

—

—

—

166

—

0.192

—

—

—

133

UI

UI

UI

UI

4

0.668

0.2

0.2

95

0.668

0.2

0.2

95

0.668

0.2

0.2

95

MHz

LFEC20

LFEC20

LFEC20

—

1.19

—

420

—

250

—

1.19

—

378

—

300

—

1.19

—

340

—

350

MHz

ns

ps

t

DQVAS

t

DQVBS

DQ and DQS Write Timings

t

DQS

DQ

DQS

DQ

DVEDQ

t

DVADQ

DQ and DQS Read Timings

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LFEC33E-4F672I | LatticeECP/EC Family Data Sheet |

| LFEC33E-4F900I | ECONOLINE: RSZ/P - 1kVDC |

| LFEC33E-4Q208I | LatticeECP/EC Family Data Sheet |

| LFEC33E-4T100I | ECONOLINE: RSZ/P - 1kVDC |

| LFEC33E-4T144C | LatticeECP/EC Family Data Sheet |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LFEC33E-4F672I | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 32.8K LUTs 496 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| LFEC33E-4F900C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeECP/EC Family Data Sheet |

| LFEC33E-4F900I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeECP/EC Family Data Sheet |

| LFEC33E-4FN256C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeECP/EC Family Data Sheet |

| LFEC33E-4FN256I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeECP/EC Family Data Sheet |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。