- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄97997 > LC7185-8750 (SANYO SEMICONDUCTOR CO LTD) PLL FREQUENCY SYNTHESIZER, 30 MHz, PDIP30 PDF資料下載

參數(shù)資料

| 型號(hào): | LC7185-8750 |

| 廠(chǎng)商: | SANYO SEMICONDUCTOR CO LTD |

| 元件分類(lèi): | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 30 MHz, PDIP30 |

| 封裝: | SDIP-30 |

| 文件頁(yè)數(shù): | 2/12頁(yè) |

| 文件大?。?/td> | 152K |

| 代理商: | LC7185-8750 |

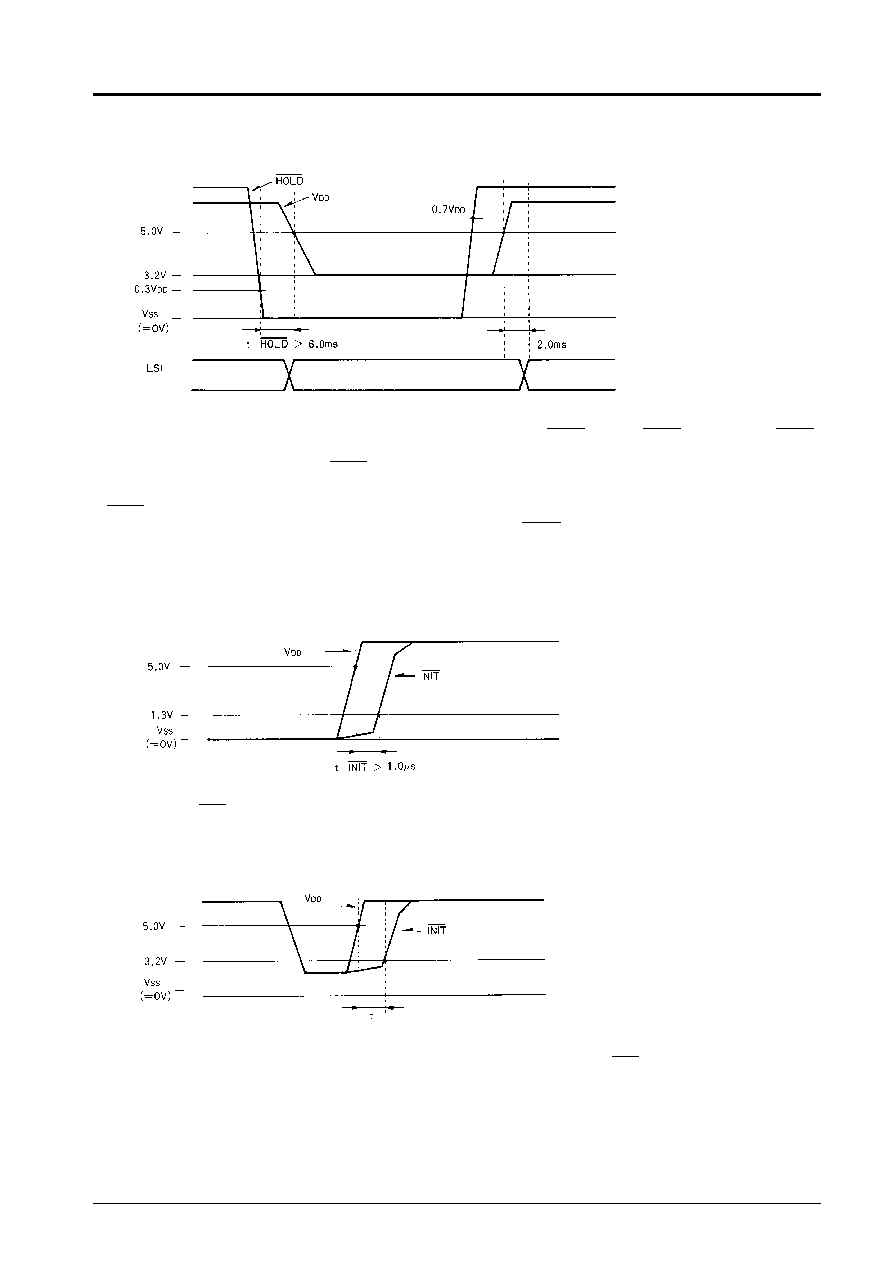

(3) Timing Requirements for Hold Mode

VDD must remain at 5.0 V or higher (crystal oscillator requirement) for 6.0 ms (t HOLD) after the HOLD line is asserted (HOLD

=0(<0.3 VDD). After this, VDD may go as low as 3.2 V.

There are no constraints on timing for the HOLD and VDD pins when the chip is leaving hold mode.

The signal can be activated in one of two orders.

If HOLD is already deactivated (> 0.7 VDD), the LC7185-8750 leaves hold mode within 2.0 ms after VDD rises to >5.0 V.

If VDD is > 5.0 V, the LC7185-8750 enters normal mode within 2.0 ms after HOLD is deactivated.

(4) Reset Timing

1.

Reset timing (e.g. battery replacement)

Note: tINIT should be greater than 1.0 s.

2.

Reset caused by a sudden voltage (VDD) drop

If VDD drops momentarily down to less than 3.2 V and rises up to more than 5.0 V t > tINIT (t > 1.0 s), a reset may be

generated.

pin

Normal mode

Hold mode

Normal mode

pin

LC7185-8750

No. 3356-10/12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC72122V | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 |

| LC72144M | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO24 |

| LC72151V | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO30 |

| LC7216M | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 |

| LCP-10G3A4EDR | FIBER OPTIC TRANSCEIVER, 840-860nm, 10312.5Mbps(Tx), 10312.5Mbps(Rx), SURFACE MOUNT, LC CONNECTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC7185-8750-E | 制造商:ON Semiconductor 功能描述:PLL FREQUENCY SYSTHESIZER - Ammo Pack |

| LC7191 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Display Driver, Other/Special/Miscellaneous |

| LC71C18 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Laser Diode with Monitor Diode |

| LC71C18G | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Laser Diode with Monitor Diode |

| LC71F7000MA0-AH | 功能描述:電容觸摸傳感器 TOUCH SENSOR IC RoHS:否 制造商:Microchip Technology 電源電壓: 通道數(shù)量: 封裝 / 箱體: 尺寸: 溫度范圍: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。