- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377611 > LC5512MC-45F256C (LATTICE SEMICONDUCTOR CORP) 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family PDF資料下載

參數(shù)資料

| 型號: | LC5512MC-45F256C |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| 中文描述: | EE PLD, 5.7 ns, PBGA256 |

| 封裝: | FPBGA-256 |

| 文件頁數(shù): | 11/92頁 |

| 文件大小: | 378K |

| 代理商: | LC5512MC-45F256C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

Lattice Semiconductor

ispXPLD 5000MX Family Data Sheet

11

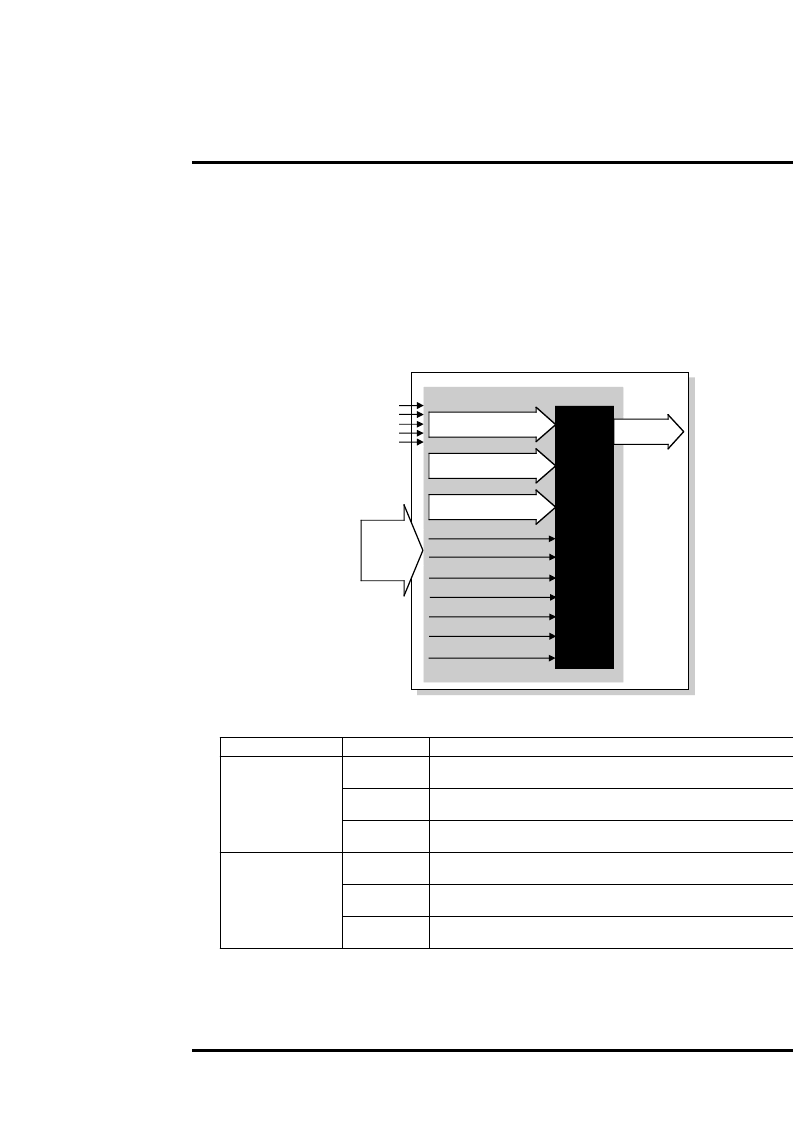

Pseudo Dual-Port SRAM Mode

In Pseudo Dual-Port SRAM Mode the multi-function array is con

fi

gured as a SRAM with an independent read and

write ports that access the same 16,384-bits of memory. Data widths of 1, 2, 4, 8, 16 and 32 are supported by the

MFB. Figure 10 shows the block diagram of the Pseudo Dual-Port SRAM.

Write data, write address, chip select and write enable signals are always synchronous (registered). The read data

and read address signals can be synchronous or asynchronous. Reset is asynchronous. All write signals share the

same clock, and clock enable. All read signals share the same clock and clock enable. Reset is shared by both

read and write signals. Table 6 shows the possible sources for the clock, clock enable and initialization signals for

the various registers.

Figure 10. Pseudo Dual-Port SRAM Block Diagram

Table 6. Register Clock, Clock Enable, and Reset in Pseudo Dual-Port SRAM Mode

Register

Input

Source

Write Address, Write

Data, Write Enable,

and Write Chip Select

Clock

WCLK or one of the global clocks (CLK0 - CLK3). The selected signal can

be inverted if desired.

WCEN or one of the global clocks (CLK1 - CLK2). The selected signal can

be inverted if desired.

Created by the logical OR of the global reset signal and RST. RST may have

inversion if desired.

RCLK or one of the global clocks (CLK0 - CLK3). The selected signal can be

inverted if desired.

RCEN or one of the global clocks (CLK1 - CLK2). The selected signal can

be inverted if desired.

Created by the logical OR of the global reset signal and RST. RST may have

inversion if desired.

Clock Enable

Reset

Read Data and Read

Address

Clock

Clock Enable

Reset

‘

‘

68 Inputs

From

Routing

16,384 bi

t

Pseudo

Dual

Port

SRAM

Array

Write Address

(WAD[0:8-13])

Write Clk Enable

(WCEN)

Write Clock

(WCLK)

Write Chip Sel

(WCS[0,1])

Read Address

(RAD[0:8-13])

Write Enable

(WE)

Reset

(RST)

Read Clk Enable

(RCEN)

Read Clock

(RCLK)

Write Data

(WD[0:0,1,3,7,15,31])

RESET

CLK0

CLK1

CLK2

Read Data

(RD[0:0-15])

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC5512MC-45F484C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-45Q208C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75F256C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75F484C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75Q208C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC5512MC-45F256I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-45F484C | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC5512MC-45F484I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-45F672C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-45F672I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。