- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369719 > LC4132C PDF資料下載

參數(shù)資料

| 型號: | LC4132C |

| 文件頁數(shù): | 3/12頁 |

| 文件大小: | 102K |

| 代理商: | LC4132C |

No. 6477-3/12

LC4132C

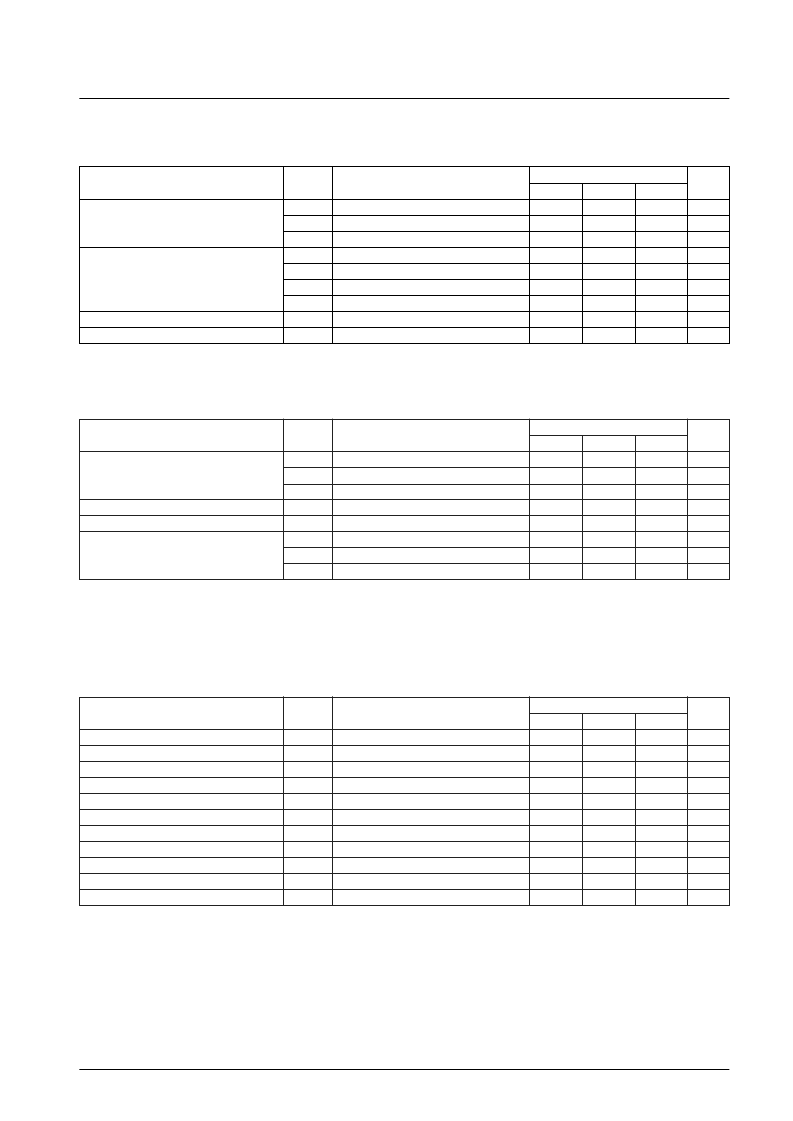

The electrical characteristics listed below apply when packaged in the Sanyo PGA-208 package.

Notes: 1. D0 to D7, LOAD, CP, R/L, DISP, M, EIO1, EIO2, BS

2. The following relationships must hold for V0, V2, V3, and V5: V

DDH

≥

V0

≥

V2

≥

V

DDH

– 7 V, and 7 V

≥

V3

≥

V5

≥

V

SS

.

Notes: 3. D0 to D7, LOAD, CP, R/L, M, DISP, BS, EIO1, EIO2

4. The following relationships must hold for V0, V2, V3, and V5: V

DDH

≥

V0

≥

V2

≥

V

DDH

– 7 V, and 7 V

≥

V3

≥

V5

≥

V

SS

.

At power on: The logic system power supply must be applied before the high-voltage system power supply. (Or they must both be applied at the

same time.)

At power off: The high-voltage system power supply must be turned off before the logic system power supply. (Or they must both be turned off at

the same time.)

Note: 5. The clock rise time (tr) and the clock fall time (tf) must meet the conditions (1) and (2) shown below.

1

fcp

(1) tr, tf < ————————————

(2) tr, tf

≤

50 ns

2

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

V

DD

max

V

DDH

max V

DDH

V

SS

max

V

IN

V0, V2

V

DD

–0.3

7.0

V

Maximum supply voltage

–0.3

40.0

V

V

SS

*

1

–0.3

0.3

V

–0.3

V

DD

+ 0.3

V

DDH

+ 0.3

V

SS

+ 7.0

V

Input voltage

V0, V2

*

2

V

DDH

– 7.0

V

V3

V3

*

2

–0.3

V

V5

V5

*

2

–0.3

0.3

V

Operating temperature

Topr

–20

+75

°C

Storage temperature

Tstg

–55

+125

°C

Absolute Maximum Ratings

at V

SS

= 0 V

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

V

DD

V

DDH

V

SS

V

IH

V

IL

V0, V2

V

DD

V

DDH

V

SS

*

3

2.7

5.5

V

Supply voltage

20

36

V

0

V

Input high-level voltage

0.8 V

DD

V

DD

V

Input low-level voltage

*

3

0

0.2 V

DD

V

DDH

V

SSH

+ 7.0

V

V0, V2

*

4

V

DDH

– 7.0

V

Input voltage

V3

V3

*

4

0

V

V5

V5

*

1

0

V

Allowable Operating Ranges

at Ta = –20 to +75°C, V

SS

= 0 V

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

CP clock frequency

fcp

CP

12

MHz

High-level load pulse width

tw (ldH)

LOAD

50

ns

High-level clock pulse width

tw (cpH)

CP

20

ns

Low-level clock pulse width

tw (cpL)

CP

20

ns

LOAD/CP setup time

tsu (ld)

LOAD, CP

100

ns

LOAD/CP hold time

tho (ld)

LOAD, CP

200

ns

DATA/CP setup time

tsu (cp)

CP, D0 to D7

10

ns

DATA/CP hold time

tho (cp)

CP, D0 to D7

10

ns

EIO input setup time

tsu (ei)

CP, EIO1, EIO2

24

ns

Clock rise time

tr

LOAD, CP

*

5

50

ns

Clock fall time

tf

LOAD, CP

*

5

50

ns

V

DD

= 5 V ±10%, Ta = –20 to +75°C, V

SS

= 0 V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC4528B | Logic IC |

| LC507 | High Gain Class A Amplifier |

| LC507MCRO | Hearing Aid Amplifier |

| LC507PLID | Hearing Aid Amplifier |

| LC508MCRO | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC41387KBR-X2T | 制造商:ON Semiconductor 功能描述:LCD DRIVER ICS - Waffle Pack |

| LC41388KBR-X2T | 制造商:ON Semiconductor 功能描述:LCD DRIVER ICS - Waffle Pack |

| LC4141R82 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Optoelectronic |

| LC4200 | 制造商:3M Electronic Products Division 功能描述:LC4200 WSS ADHESIVE |

| LC42077-001A-A | 制造商:JVC Worldwide 功能描述:LAMP DOOR SCREW |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。