- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358754 > LC36256ALL-70W (Sanyo Electric Co.,Ltd.) 256 K (32768 words x 8 bits) SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | LC36256ALL-70W |

| 廠商: | Sanyo Electric Co.,Ltd. |

| 英文描述: | 256 K (32768 words x 8 bits) SRAM |

| 中文描述: | 256度(32768字× 8位)的SRAM |

| 文件頁數(shù): | 1/7頁 |

| 文件大?。?/td> | 99K |

| 代理商: | LC36256ALL-70W |

Ordering number : EN4163A

22896HA (OT)/21593JN (OT) No. 4163-1/7

Overview

The LC36256AL, AML are fully asynchronous silicon

gate CMOS static RAMs with an 32768 words

×

8 bits

configuration.

This series have CE chip enable pin for device

select/nonselect control and an OE output enable pin for

output control, and features high speed as well as low

power dissipation.

For these reasons, the series is especially suited for use in

systems requiring high speed, low power, and battery

backup, and it is easy to expand memory capacity.

Features

Access time

70

ns (max.) : LC36256AL-70, LC36256AML-70

85

ns (max.) : LC36256AL-85, LC36256AML-85

100 ns (max.) : LC36256AL-10, LC36256AML-10

120 ns (max.) : LC36256AL-12, LC36256AML-12

Low current dissipation

During standby

2

μA (max.) / Ta = 25°C

5

μA (max.) / Ta = 0 to +40°C

25 μA (max.) / Ta = 0 to +70°C

During data retention

1

μA (max.) / Ta = 25°C

2

μA (max.) / Ta = 0 to +40°C

10 μA (max.) / Ta = 0 to +70°C

During operation (DC)

10 mA (max.)

Single 5 V power supply: 5 V ±10%

Data retention power supply voltage: 2.0 to 5.5 V

No clock required (Fully static memory)

All input/output levels are TTL compatible

Common input/output pins, with three output states

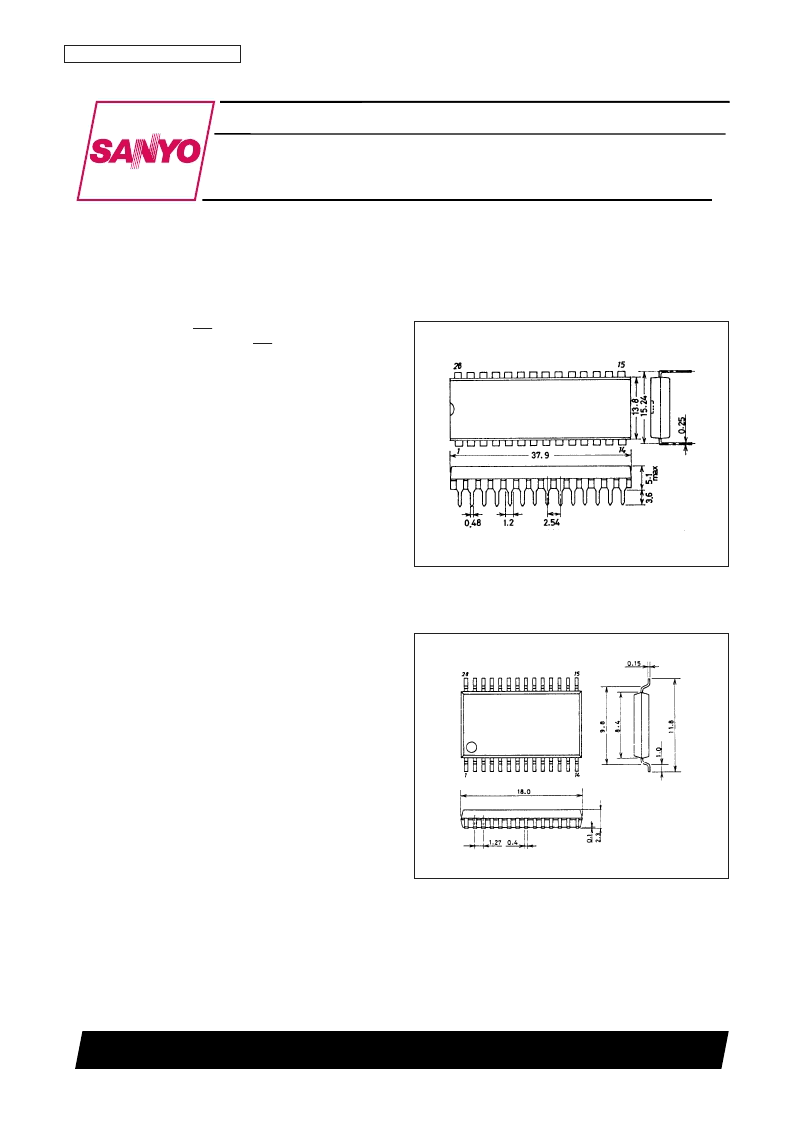

Packages

DIP 28 -pin (600 mil) plastic package : LC36256AL

SOP 28-pin (450 mil) plastic package : LC36256AML

Package Dimensions

unit: mm

3012A - DIP28

unit : mm

3187 - SOP28D

SANYO: DIP28

[LC36256AL]

SANYO: SOP28D

[LC36256AML]

LC36256AL, AML-70/85/10/12

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-0005 JAPAN

256 K (32768 words

×

8 bits) SRAM

Asynchronous Silicon Gate CMOS LSI

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC36256ALL-85W | 256 K (32768 words x 8 bits) SRAM |

| LC36256AL-10 | 256 K (32768 words x 8 bits) SRAM |

| LC36256AL-12 | 256 K (32768 words x 8 bits) SRAM |

| LC36256AL-70 | 256 K (32768 words x 8 bits) SRAM |

| LC3664AML | CMOS LSI 64K SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC36256ALL-85 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LC36256ALL-85W | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:256 K (32768 words x 8 bits) SRAM |

| LC36256ALLW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LC36256ALW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LC36256AML | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。