- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358741 > LAN83C183-JD (STANDARD MICROSYSTEMS CORP) FAST ETHERNET PHYSICAL LAYER DEVICE PDF資料下載

參數(shù)資料

| 型號: | LAN83C183-JD |

| 廠商: | STANDARD MICROSYSTEMS CORP |

| 元件分類: | 網(wǎng)絡(luò)接口 |

| 英文描述: | FAST ETHERNET PHYSICAL LAYER DEVICE |

| 中文描述: | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| 封裝: | 1.40 MM HEIGHT, LQFP-64 |

| 文件頁數(shù): | 9/22頁 |

| 文件大小: | 166K |

| 代理商: | LAN83C183-JD |

SMSC DS – LAN83C180

Page 9

Rev. 08/24/2001

the reference until the equalizer has adjusted, then it requires up to 1ms to phase lock to the incoming signal. No

data is passed to the MII interface until lock is established.

RX100 SIPO, Decoder and Descrambler

The RX100 SIPO, Decoder and descrambler convert the received signal from serial MLT3 to 4-bit wide parallel

receive data on the MII. This appears on the RXD[3:0] bus which is clocked out on the rising edge of RX_CLK. When

a frame starts the LAN83C180 decodes the SSD symbols and then asserts the RX_DV signal, in order to inform the

MAC that valid data is available. When the LAN83C180 detects the ESD, it deasserts the RX_DV signal.

RX100 Latency

The latency from the first bit of the “J” symbol on the cable to CRS assertion is between 11 and 15BT. The latency

from the first bit of the “T” symbol on the cable to CRS de-assertion is between 19 and 23BT.

100Mb/s Transmit Errors

If the LAN83C180 detects that the TX_ER signal has gone active while the TX_EN signal is active, then it will

propagate the detected error onto the cable by transmitting the symbol “00100”. Table 1 shows the meaning of the

different states of TX_EN and TX_ER. TX_ER is sampled inside the LAN83C180 on the rising edge of TX_CLK.

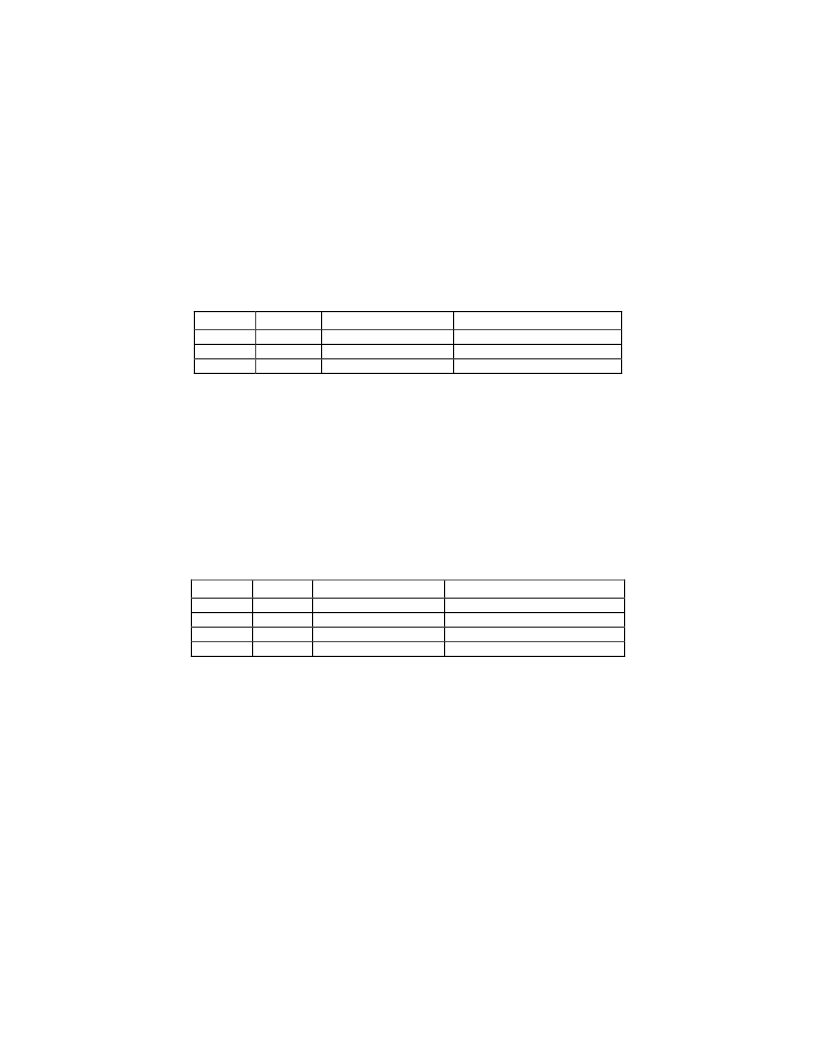

Table 1 - 100MB/S Transmit Error States

TX_ER

TXD [3:0]

X

Ignored

0

0000 Through 1111

1

0000 Through 1111

TX_EN

0

1

1

INDICATION

Normal Inter Frame Data

Normal Data Transmission

Transmit Error Propagation

100Mb/s Receive Errors

When there is no data on the cable, the receiver will see only the idle code of scrambled 1’s. If a non idle symbol is

detected, the receiver looks for the SSD so that it can align the incoming message for decoding. If any 2 non

consecutive zeros are detected within 10 bits, but are not the SSD symbols a false carrier indication is signaled to

the MII by asserting RX_ER and setting RXD[3:0] to 1110 while keeping RX_DV inactive. The remainder of the

message is ignored until 10 bits of 1’s are detected.

If any data is decoded after a SSD which is neither a valid data code nor an ESD, then an error is flagged by setting

RX_ER active while the RX_DV signal is active. This also happens if 2 idle codes are detected before a valid ESD

has been received –or- descramble synchronization is lost during packet reception. The states of RX_DV and

RX_ER are summarized in Table 2. RX_ER is clocked on the falling edge of RX_CLK, and will remain active for at

least 1 period of RX_CLK.

Table 2 - 100MB/S Receive Error States

RX_ER

RXD [3:0]

0

0000 Through 1111

1

1110

0

0000 Through 1111

1

0101 or 0110

RX_DV

0

0

1

1

INDICATION

Normal Inter Frame

False Carrier Indication

Normal Data Reception

Data Reception With Errors

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN83C180TQFP | 10/100 FAST ETHERNET PHY TRANSCEIVER |

| LAN83C183 | FAST ETHERNET PHYSICAL LAYER DEVICE |

| LAN83C185-JD | HIGH PERFORMANCE SINGLE CHIP LOW POWER 10/100 ETHERNET PHYSICAL LAYER TRANSCEIVER |

| LAN83C185-JT | HIGH PERFORMANCE SINGLE CHIP LOW POWER 10/100 ETHERNET PHYSICAL LAYER TRANSCEIVER |

| LAN8700 | 【15kV ESD Protected MII/RMII Fast-Ethernet PHY with HP Auto-MDIX and SMSC flexPWR TM in a Small Footprint |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN83C185 | 制造商:SMSC 制造商全稱:SMSC 功能描述:High Performance Single Chip Low Power 10/100 Ethernet Physical Layer Transceiver |

| LAN83C185_03 | 制造商:SMSC 制造商全稱:SMSC 功能描述:High Performance Single Chip Low Power 10/100 Ethernet Physical Layer Transceiver |

| LAN83C185-JD | 功能描述:電信線路管理 IC Lo Pwr 10/100 3.3V PHY RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| LAN83C185JT | 制造商:SMSC 功能描述: |

| LAN83C185-JT | 功能描述:電信線路管理 IC Ethernet IC PHY RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。