- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377595 > L4C381JC20 (LOGIC DEVICES INC) 16-bit Cascadable ALU PDF資料下載

參數(shù)資料

| 型號: | L4C381JC20 |

| 廠商: | LOGIC DEVICES INC |

| 元件分類: | 位片處理器 |

| 英文描述: | 16-bit Cascadable ALU |

| 中文描述: | 16-BIT, BIT-SLICE MICROPROCESSOR, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 1/12頁 |

| 文件大小: | 85K |

| 代理商: | L4C381JC20 |

DEVICES INCORPORATED

L4C381

16-bit Cascadable ALU

16-bit Cascadable ALU

Arithmetic Logic Units

08/16/2000–LDS.381-P

1

K

High-Speed (15ns), Low Power

16-bit Cascadable ALU

K

Implements Add, Subtract, Accumu-

late, Two’s Complement, Pass, and

Logic Operations

K

All Registers Have a Bypass Path

for Complete Flexibility

K

68-pin PLCC, J-Lead

FEATURES

DESCRIPTION

DEVICES INCORPORATED

L4C381 B

LOCK

D

IAGRAM

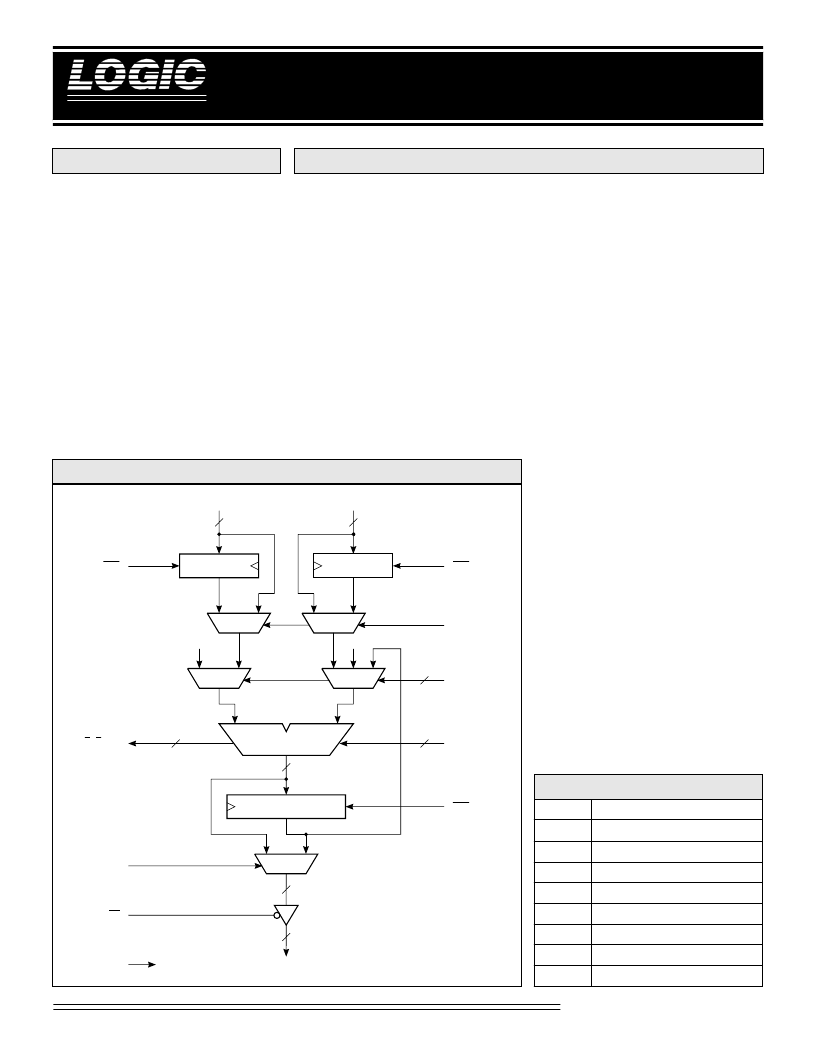

The

L4C381

is a flexible, high speed,

cascadable 16-bit Arithmetic and

Logic Unit. It combines four 381-type

4-bit ALUs, a look-ahead carry

generator, and miscellaneous interface

logic — all in a single 68-pin package.

While containing new features to

support high speed pipelined architec-

tures and single 16-bit bus configura-

tions, the L4C381 retains full perform-

ance and functional compatibility with

the bipolar ’381 designs.

The L4C381 can be cascaded to

perform 32-bit or greater operations.

See “Cascading the L4C381” toward

the end of this data sheet for more

information.

ARCHITECTURE

The L4C381 operates on two 16-bit

operands (A and B) and produces a

16-bit result (F). Three select lines

control the ALU and provide 3

arithmetic, 3 logical, and 2 initializa-

tion functions. Full ALU status is

provided to support cascading to

longer word lengths. Registers are

provided on both the ALU inputs and

the output, but these may be bypassed

under user control. An internal

feedback path allows the registered

ALU output to be routed to one of the

ALU inputs, accommodating chain

operations and accumulation. Fur-

thermore, the A or B input can be

forced to Zero allowing unary func-

tions on either operand.

ALU OPERATIONS

The S

2

–S

0

lines specify the operation

to be performed. The ALU functions

and their select codes are shown in

Table 1.

The two functions, B minus A and

A minus B, can be achieved by setting

the carry input of the least significant

slice and selecting codes 001 and 010

respectively.

S

2

-S

0

FUNCTION

000

CLEAR (F = 00

00)

001

NOT(A) + B

010

A + NOT(B)

011

A + B

100

A XOR B

101

A OR B

110

A AND B

111

PRESET (F = 11

11)

T

ABLE

1.

A

LU

F

UNCTIONS

A REGISTER

B REGISTER

ALU

RESULT REGISTER

A

15

-A

0

B

15

-B

0

F

15

-F

0

0

0

ENB

FTAB

OSA

OSB

S

2

-S

0

, C

0

P, G, C

16

OVF, Z

ENF

FTF

OE

CLK

ENA

16

16

4

5

16

16

16

TO ALL REGISTERS

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| L4C383JC20 | 16-bit Cascadable ALU (Extended Set) |

| L4C383JC26 | 16-bit Cascadable ALU (Extended Set) |

| L4C383 | 16-bit Cascadable ALU (Extended Set) |

| L514-G | MR11 and MR16 Halogen Lamps with Gold Coated Reflectors |

| L515-G | MR11 and MR16 Halogen Lamps with Gold Coated Reflectors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| L4C381JC26 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fixed Point ALU |

| L4C381JC40 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fixed Point ALU |

| L4C381JC55 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fixed Point ALU |

| L4C381KC15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fixed Point ALU |

| L4C381KC20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fixed Point ALU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。