- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383234 > L4990A (意法半導(dǎo)體) PRIMARY CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | L4990A |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | PRIMARY CONTROLLER |

| 中文描述: | 主控制器 |

| 文件頁數(shù): | 3/24頁 |

| 文件大?。?/td> | 322K |

| 代理商: | L4990A |

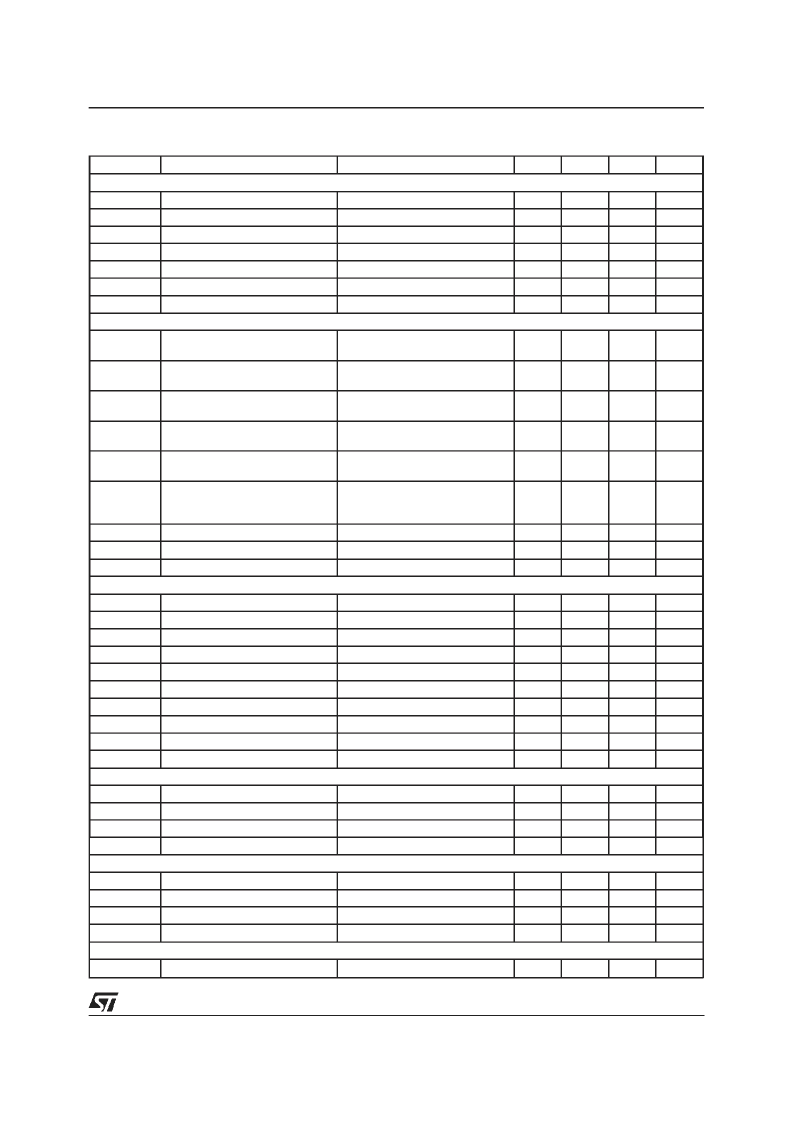

ELECTRICALCHARACTERISTICS

(V

CC

= 15V; T

j

= 0 to 70

°

C; unless otherwise specified.)

Symbol

REFERENCE SECTION

V

O

Parameter

Test Condition

Min.

Typ.

Max.

Unit

Output Voltage

Line Regulation

Load Regulation

Temperature Stability

Total Variation

Short Circuit Current

Power Down/UVLO

T

j

= 25

°

C; I

O

= 1mA

V

CC

= 12 to 20V

I

O

= 1 to 20mA

4.925

5.0

2.0

5.0

0.4

5.0

5.075

15

20

V

mV

mV

mV/

°

C

V

mA

V

T

S

Line, Load, Temperature

Vref = 0V

V

CC

= 8.5V; I

sink

= 0.5mA

4.875

30

5.125

150

0.5

I

OS

0.2

OSCILLATOR SECTION

Initial Accuracy

T

j

= 25

°

C; R

T

= 4.42k

;

C

T

= 1nF; pin 15 Vref

R

T

= 4.42K

; V

CC

= 12 to 20V;

C

T

= 1nF; pin 15 = Vref

T

j

= 25

°

C; R

T

= 4.42K

;

C

T

= 1nF; pin 15 OPEN

R

T

= 4.42K

; V

CC

= 12 to 20V;

C

T

= 1nF; pin 15 OPEN

pin 3 = 0,7V, pin 15 = Vref

pin 3 = 0.7V, pin 15 = OPEN

R

T

= 4.42k

C

T

= 1nF

pin 3 = 3.2V, pin 15 = Vref

pin 3 = 3.2V, pin 15 = OPEN

pin 3 = 2.02V, pin 15 = OPEN

285

300

315

kHz

Accuracy

279

300

321

kHz

Initial Accuracy

280

295

310

kHz

Accuracy

275

295

315

kHz

Duty Cycle

0

0

%

%

Duty Cycle

45

90

37

%

%

%

V

V

Duty Cycle Accuracy

Oscillator Ramp Peak

Oscillator Ramp Valley

40

3.0

1.0

43

ERROR AMPLIFIER SECTION

Input Bias Current

V

I

Input Voltage

G

OPL

Open Loop Gain

SVR

Supply Voltage Rejection

V

OL

Output Low Voltage

V

OH

Output High Voltage

I

O

Output Source Current

Output Sink Current

Unit Gain Bandwidth

S

R

Slew Rate

PWM CURRENT SENSE SECTION

I

b

Input Bias Current

I

S

Maximum Input Signal

Delay to Output

Gain

SOFT START

I

SSC

SS Charge Current

I

SSD

SS Discharge Current

V

SSSAT

SS Saturation Voltage

V

SSCLAMP

SS Clamp Voltage

LEADING EDGE BLANKING

Internal Masking Time

V

FB

to GND

V

COMP

= V

FB

V

COMP

= 2to 4V

V

CC

= 12 to 20V

I

sink

= 2mA, V

FB

= 2.7V

I

source

= 0.5mA, V

FB

= 2.3V

V

COMP

> 4V,V

FB

= 2.3V

V

COMP

= 1.1V,V

FB

= 2.7V

0.2

2.5

90

85

1.0

2.58

μ

A

V

dB

dB

V

V

mA

mA

MHz

V/

μ

s

2.42

60

1.1

5

6

0.5

2

2

1.3

6

4

8

I

sen

= 0

V

COMP

= 5V

3

15

1.08

μ

A

V

ns

V/V

0.92

1.0

100

3

2.85

3.15

14

20

200

26

μ

A

μ

A

V

V

VSS = 0.6V

DC = 0%

0.6

7

100

ns

L4990 - L4990A

3/24

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| L4990AD | PRIMARY CONTROLLER |

| L4990D | PRIMARY CONTROLLER |

| L4992 | TRIPLE OUTPUT POWER SUPPLY CONTROLLER |

| L5170 | CAP CER 47000PF 50V X7R 0805 |

| L5170A | OCTAL LINE DRIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| L4990AD | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:PRIMARY CONTROLLER |

| L4990D | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:PRIMARY CONTROLLER |

| L4991 | 功能描述:TEST COIL FOR REED SWITCH, 1PC RoHS:是 類別:開關(guān) >> 配件 系列:- 標準包裝:100 系列:- 其它名稱:886.0007886.0007-ND |

| L4992 | 制造商:STMicroelectronics 功能描述: 制造商:STMicroelectronics 功能描述:VOLT SUPERVISOR CNTRLR 5.1V/3.3V 32TQFP - Trays |

| L4993 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Low drop voltage regulator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。