- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373089 > K9S1208V0 (SAMSUNG SEMICONDUCTOR CO. LTD.) 64MB & 128MB SmartMediaTM Card PDF資料下載

參數(shù)資料

| 型號: | K9S1208V0 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 64MB & 128MB SmartMediaTM Card |

| 中文描述: | 64MB的 |

| 文件頁數(shù): | 29/37頁 |

| 文件大小: | 657K |

| 代理商: | K9S1208V0 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

SmartMedia

TM

29

K9S1208V0M/A-SSB0

K9D1G08V0M/A-SSB0

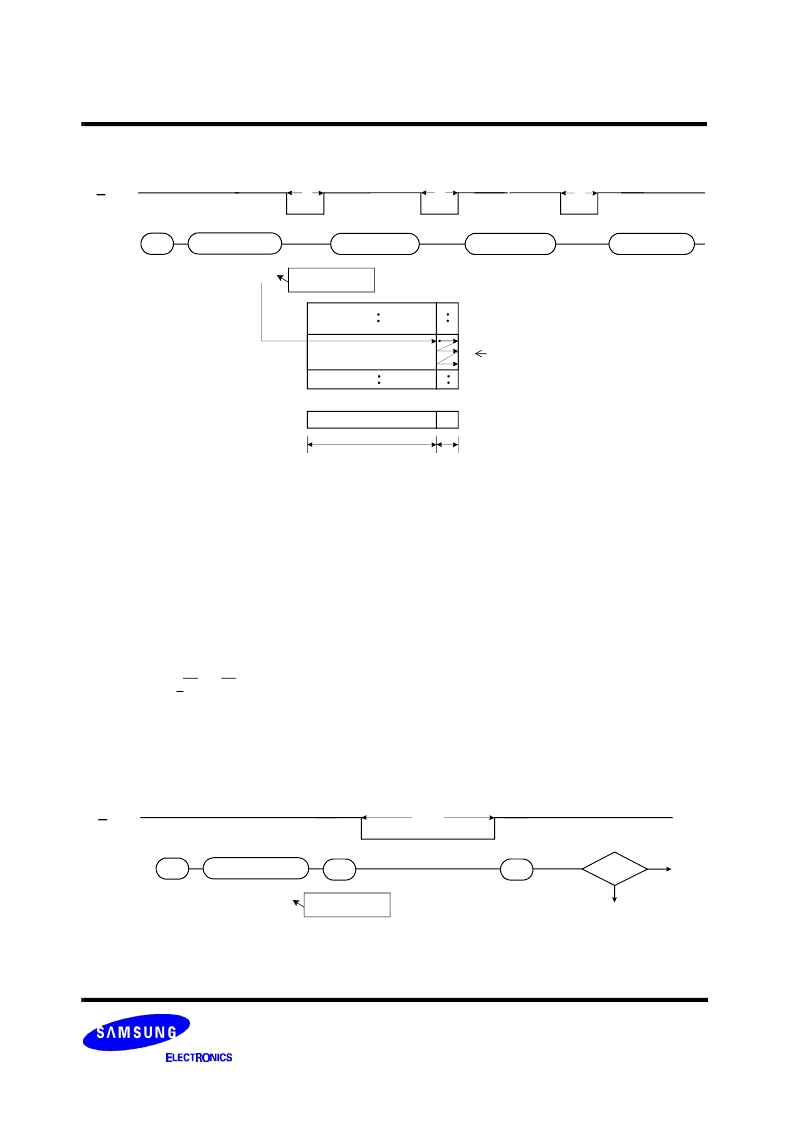

Figure 12. Sequential Row Read2 Operation

PAGE PROGRAM

The device is programmed basically on a page basis, but it does allow multiple partial page programing of a byte or consecutive bytes

up to 528, in a single page program cycle. The number of consecutive partial page programming operation within the same page with-

out an intervening erase operation must not exceed 1 for main array and 2 for spare array. However, it is advisable not to program

more often than recommend. It might cause failures due to disturbance when it exceeds its limits. The failure mode could be that the

data "1" of the erased cell might be changed into data"0"of the programmed cell.

The addressing may be done in any random order in a block. A page program cycle consists of a serial data loading period in which

up to 528 bytes of data may be loaded into the page register, followed by a non-volatile programming period where the loaded data is

programmed into the appropriate cell. Serial data loading can be started from 2nd half array by moving pointer. About the pointer

operation, please refer to the attached technical notes.

The serial data loading period begins by inputting the Serial Data Input command(80h), followed by the four cycle address input and

then serial data loading. The bytes other than those to be programmed do not need to be loaded.The Page Program confirm com-

mand(10h) initiates the programming process. Writing 10h alone without previously entering the serial data will not initiate the pro-

gramming process. The internal write-state controller automatically executes the algorithms and timings necessary for program and

verify, thereby freeing the system controller for other tasks. Once the program process starts, the Read Status Register command

may be entered, with RE and CE low, to read the status register. The system controller can detect the completion of a program cycle

by monitoring the R/B output, or the Status bit(I/O 6) of the Status Register. Only the Read Status command and Reset command are

valid while programming is in progress. When the Page Program is complete, the Write Status Bit(I/O 0) may be checked(Figure 13).

The internal write verify detects only errors for "1"s that are not successfully programmed to "0"s. The command register remains in

Read Status command mode until another valid command is written to the command register.

50h

A

0

~ A

3

& A

9

~ A

26

I/O

0

~

7

R/B

Start Add.(4Cycle)

Data Output

Data Output

Data Output

2nd

Nth

(16Byte)

(16Byte)

1st

Figure 13. Program & Read Status Operation

80h

A

0

~ A

7

& A

9

~ A

26

528 Byte Data

I/O

0

~

7

R/B

Address & Data Input

I/O

0

Pass

10h

70h

Fail

t

R

t

R

t

R

t

PROG

≈

Data Field

Spare Field

1st

Block

Nth

(A

4

~ A

7

:

Don

t Care)

A

25

: K9S1208V0X

A

26

: K9D1G08V0X

A

25

: K9S1208V0X

A

26

: K9D1G08V0X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K9D1G08V0M | 64MB & 128MB SmartMediaTM Card |

| K9S6408V0A-SSB0 | 8M x 8 Bit SmartMediaTM Card |

| KA-3020 | 3x2mm SINGLE COLOR SURFACE MOUNT LED LAMPS |

| KA-3020EC | 3x2mm SINGLE COLOR SURFACE MOUNT LED LAMPS |

| KA-3020IT | 3x2mm SINGLE COLOR SURFACE MOUNT LED LAMPS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K9S1208V0M/A-SSB0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:64MB & 128MB SmartMediaTM Card |

| K9S1208V0M-SSB0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:64M x 8 Bit SmartMedia Card |

| K9S2808V0B | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:SmartMedia CARD |

| K9S2808V0C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:SmartMedia CARD |

| K9S2808V0M | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:16M x 8 Bit SmartMedia Card |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。