- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384538 > ISPLSI2032-80LJI (LATTICE SEMICONDUCTOR CORP) In-System Programmable High Density PLD PDF資料下載

參數(shù)資料

| 型號: | ISPLSI2032-80LJI |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | In-System Programmable High Density PLD |

| 中文描述: | EE PLD, 18.5 ns, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 6/15頁 |

| 文件大?。?/td> | 153K |

| 代理商: | ISPLSI2032-80LJI |

Specifications

ispLSI 2032/A

6

USEispLS 2032EFORNEWDESGNS

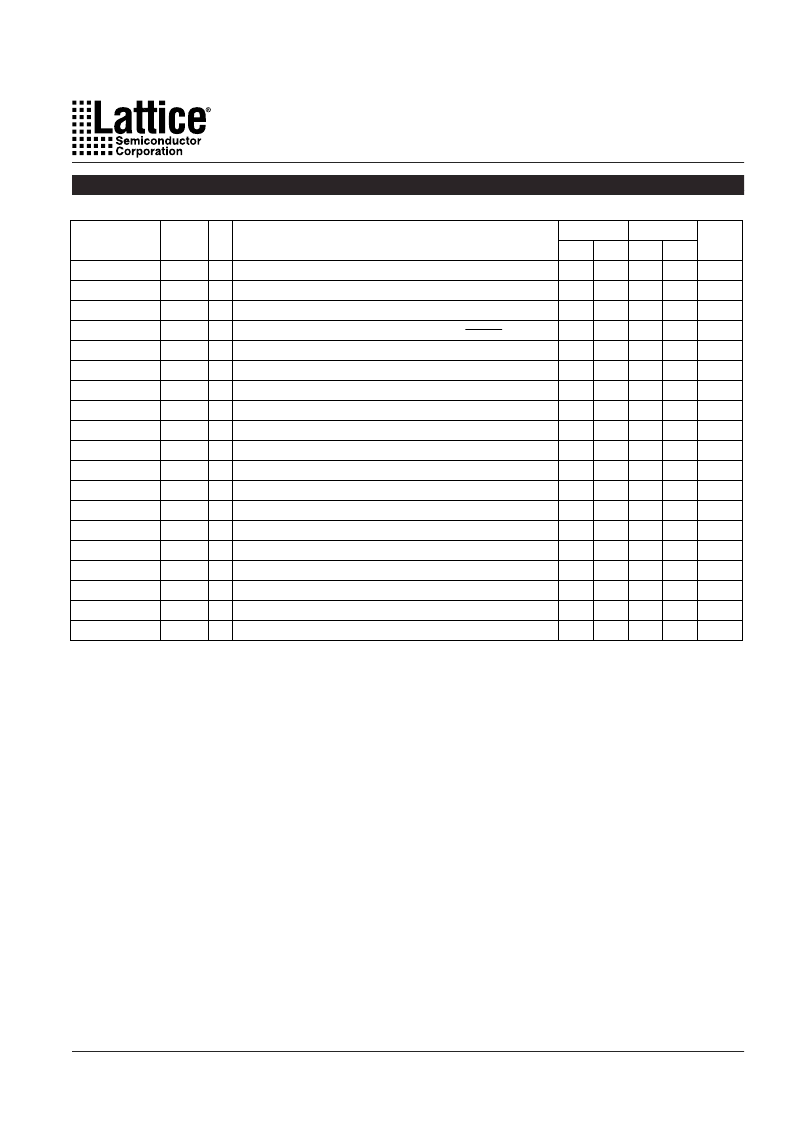

External Timing Parameters

Over Recommended Operating Conditions

t

t

pd2

f

max

f

max (Ext.)

f

max (Tog.)

t

su1

t

co1

t

h1

t

su2

t

co2

t

h2

t

r1

t

rw1

t

ptoeen

t

ptoedis

t

goeen

t

goedis

t

wh

t

wl

UNITS

-110

MIN.

–

111

TEST

COND.

1. Unless noted otherwise, all parameters use the GRP, 20 PTXOR path, ORP and Y0 clock.

2. Refer to Timing Model in this data sheet for further details.

3. Standard 16-bit counter using GRP feedback.

4. Reference Switching Test Conditions section.

Table 2-0030B-110/2032

1

4

1

tsu2 + tco1

( )

-80

MIN.

–

84.0

MAX.

13.0

MAX.

18.5

DESCRIPTION

#

2

PARAMETER

A

A

Data Propagation Delay

Clock Frequency with Internal Feedback

ns

MHz

–

–

–

–

–

A

–

4

5

6

7

8

Clock Frequency with External Feedback

Clock Frequency, Max. Toggle

GLB Reg. Setup Time before Clock, 4 PT Bypass

GLB Reg. Clock to Output Delay, ORP Bypass

GLB Reg. Hold Time after Clock, 4 PT Bypass

–

–

–

5.5

–

–

–

–

8.0

MHz

MHz

ns

ns

ns

–

–

0.0

0.0

–

–

–

–

A

–

B

C

B

C

9

GLB Reg. Setup Time before Clock

GLB Reg. Clock to Output Delay

GLB Reg. Hold Time after Clock

Ext. Reset Pin to Output Delay

Ext. Reset Pulse Duration

Input to Output Enable

Input to Output Disable

Global OE Output Enable

Global OE Output Disable

7.5

–

0.0

–

6.5

–

–

–

–

–

9.5

ns

ns

ns

ns

ns

ns

ns

ns

ns

10

11

12

13

14

15

16

17

–

0.0

–

–

–

–

–

–

–

–

–

18

19

External Synchronous Clock Pulse Duration, High

External Synchronous Clock Pulse Duration, Low

4.0

4.0

–

–

–

–

ns

ns

77.0

125

5.5

–

6.5

–

13.5

–

14.5

14.5

7.0

7.0

57.0

83.0

7.5

9.5

10.0

6.0

6.0

19.5

24.0

24.0

12.0

12.0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPLSI2032-80LT44 | In-System Programmable High Density PLD |

| ISPLSI2032-80LT44I | In-System Programmable High Density PLD |

| ISPLSI2032-80LT48 | In-System Programmable High Density PLD |

| ISPLSI2032-80LT48I | In-System Programmable High Density PLD |

| ISPLSI2032A | In-System Programmable High Density PLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPLSI2032-80LT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable Complex PLD |

| ispLSI2032-80LT44 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 USE ispMACH 4000V RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI-2032-80LT44I | 制造商:Rochester Electronics LLC 功能描述: 制造商:Lattice Semiconductor Corporation 功能描述: |

| ispLSI2032-80LT44I | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 USE ispMACH 4000V RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ISPLSI2032-80LT48 | 制造商:Lattice Semiconductor Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。