- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360914 > IQX128B-PQ184 User Programmable Special Function ASIC PDF資料下載

參數(shù)資料

| 型號(hào): | IQX128B-PQ184 |

| 英文描述: | User Programmable Special Function ASIC |

| 中文描述: | 用戶可編程ASIC的特殊功能 |

| 文件頁數(shù): | 1/65頁 |

| 文件大小: | 620K |

| 代理商: | IQX128B-PQ184 |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

IQX Family Data Sheet

June 2000

Revision 5.0

1

F

EATURES

SRAM-based, in-systemprogrammable

Switch Matrix

— Non-Blocking

— Identical and predictable delays

— One-to-one, one-to-many and many-to-one connections

RapidConfigure parallel interface for fast, incremental

configuration of Switch Matrix and I/O Port attributes

— 100% JTAG compliant

Clocked, Latched and Flow-through Dataflow Modes

— As low as 7.5 ns pin-to-pin delay in flow-through mode

and 133 MHz clock rate in registered mode

I/O Ports

— Individually programmable as input, output or

bidirectional

— For each I/O Port, clock, clock enable, input enable and

output enable can be selected independently froma large

pool of common control signals

— 12 mA current drive

— Separated I/O power pins for easy interfacing between

5V and 3.3V signals

D

ESCRIPTION

The IQX famly of SRAM-based bit-oriented switching devices is

manufactured using a 0.6μmCMOS process. These devices

offer clock speeds of up to 133 MHz and pin-to-pin delay as low

as 7.5 ns.

The IQX devices are used in applications requiring dynamc

switching and flexible routing / interconnection of signals. These

applications include communication switches, network systems,

DSP / image processing engines and file/video servers.

At the heart of IQX devices is a non-blocking Switch Matrix. A

line in the Switch Matrix can be connected to one or more other

lines. The Switch Matrix lines are connected to I/O Ports with

programmable functional attributes.

The RapidConfigure parallel interface allows connections in the

Switch Matrix to be changed quickly and incrementally. This

interface can also be used to configure I/O Port attributes

individually and incrementally. In either case, data integrity is

maintained on all unchanged signal paths through the device.

The IQX devices support the industry standard JTAG (IEEE

1149.1) interface for boundary scan testing. The same interface

can also used for serially downloading the configuration bit

streaminto the devices.

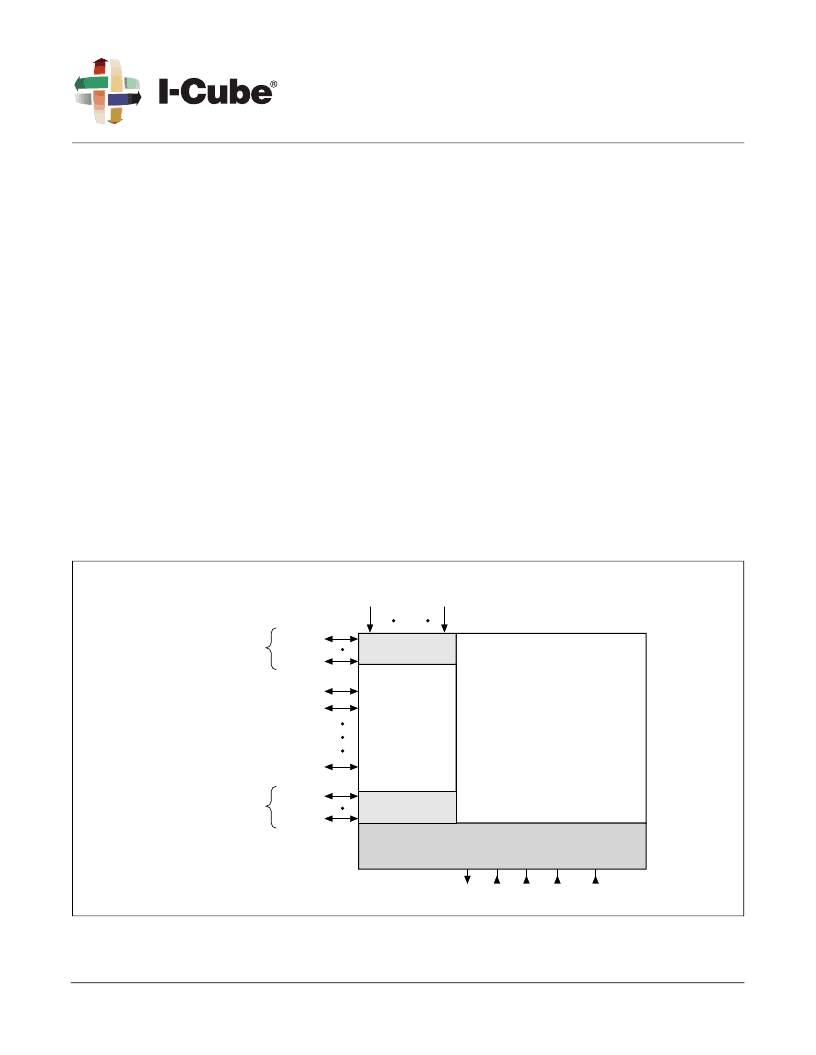

Figure 1. IQX Functional Block Diagram

I/O Port

I/O

Control

Switch Matrix

[Crossbar Array]

JTAG Configuration Control

Signal

Ports

TDI TMS TCK

TDO

I/O Port

I/O Port

RapidConfigure

Interface

I/O Port

I/O Port

I/O Port

I/O Port

Shared with

I/O Control

Signals

Dedicated

I/O Control Signals

TRST*

Shared with

RapidConfigure

Interface Signals

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IQX160-7PQ208 | User Programmable Special Function ASIC |

| IQX160-PQ208 | User Programmable Special Function ASIC |

| IQX320-10PB416 | User Programmable Special Function ASIC |

| IQX320-10PP391 | User Programmable Special Function ASIC |

| IQX320-10PP391I | User Programmable Special Function ASIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IQX160PQ208 | 制造商:I-CUBE 功能描述:New 制造商:ICUBE 功能描述: |

| IQXO-22C-24.0 | 制造商:IQD Frequency Products 功能描述:OSCILLATOR CRYSTAL |

| IQXO-22C-32MHZ | 制造商:IQD Frequency Products 功能描述:OSCILLATOR CRYSTAL |

| IQXO-22C-4.0 | 制造商:IQD Frequency Products 功能描述:OSCILLATOR CRYSTAL |

| IQXO-22C-50.0 | 制造商:IQD Frequency Products 功能描述:OSCILLATOR CRYSTAL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。