- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄3768 > IQ82C55AZ96 (Intersil)IC I/O EXPANDER 24B 44MQFP PDF資料下載

參數(shù)資料

| 型號(hào): | IQ82C55AZ96 |

| 廠商: | Intersil |

| 文件頁數(shù): | 2/29頁 |

| 文件大小: | 0K |

| 描述: | IC I/O EXPANDER 24B 44MQFP |

| 標(biāo)準(zhǔn)包裝: | 500 |

| 接口: | 可編程 |

| 輸入/輸出數(shù): | 24 |

| 中斷輸出: | 無 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 44-QFP |

| 供應(yīng)商設(shè)備封裝: | 44-MQFP(10x10) |

| 包裝: | 管件 |

第1頁當(dāng)前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

10

FN2969.10

November 16, 2006

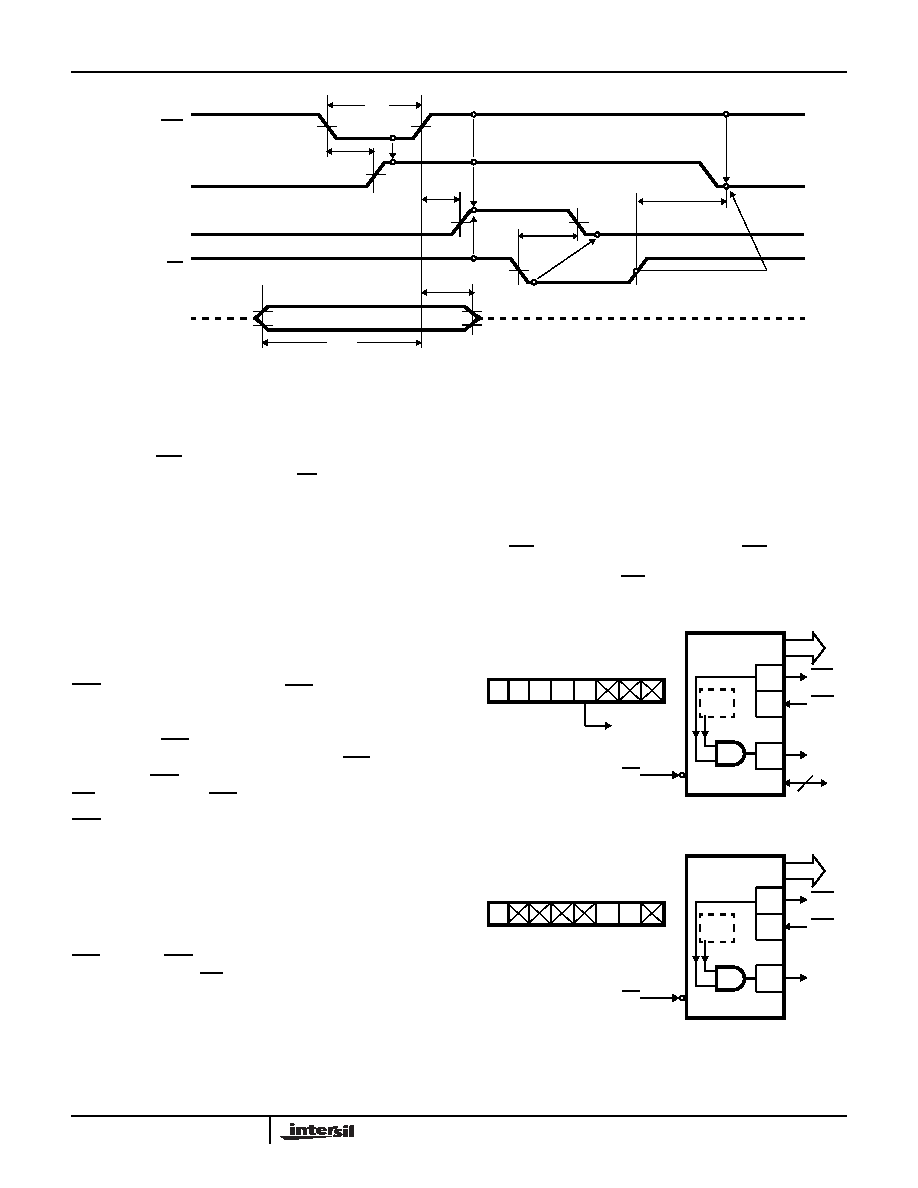

INTR (Interrupt Request)

A “high” on this output can be used to interrupt the CPU

when an input device is requesting service. INTR is set by

the condition: STB is a “one”, IBF is a “one” and INTE is a

“one”. It is reset by the falling edge of RD. This procedure

allows an input device to request service from the CPU by

simply strobing its data into the port.

INTE A

Controlled by bit set/reset of PC4.

INTE B

Controlled by bit set/reset of PC2.

Output Control Signal Definition

(Figure 8 and 9)

OBF - (Output Buffer Full F/F). The OBF output will go “l(fā)ow”

to indicate that the CPU has written data out to the specified

port. This does not mean valid data is sent out of the port at

this time since OBF can go true before data is available.

Data is guaranteed valid at the rising edge of OBF, (See

Note 1). The OBF F/F will be set by the rising edge of the

WR input and reset by ACK input being low.

ACK - (Acknowledge Input). A “l(fā)ow” on this input informs the

82C55A that the data from Port A or Port B is ready to be

accepted. In essence, a response from the peripheral device

indicating that it is ready to accept data, (See Note 1).

INTR - (Interrupt Request). A “high” on this output can be

used to interrupt the CPU when an output device has

accepted data transmitted by the CPU. INTR is set when

ACK is a “one”, OBF is a “one” and INTE is a “one”. It is reset

by the falling edge of WR.

INTE A

Controlled by Bit Set/Reset of PC6.

INTE B

Controlled by Bit Set/Reset of PC2.

NOTE:

1. To strobe data into the peripheral device, the user must operate

the strobe line in a hand shaking mode. The user needs to send

OBF to the peripheral device, generates an ACK from the

peripheral device and then latch data into the peripheral device

on the rising edge of OBF.

FIGURE 7. MODE 1 (STROBED INPUT)

tST

STB

INTR

RD

INPUT FROM

IBF

PERIPHERAL

tSIB

tSIT

tPH

tPS

tRIT

tRIB

FIGURE 8. MODE 1 OUTPUT

1

D7

0

D6

1

D5

1

D4

1/0

D3 D2 D1 D0

CONTROL WORD

MODE 1 (PORT A)

PC7

8

ACKA

PC6

PA7-PA0

OBFA

INTRA

PC3

PC4, PC5

2

WR

PC4, PC5

1 = INPUT

0 = OUTPUT

1

D7 D6 D5 D4 D3 D2 D1 D0

CONTROL WORD

MODE 1 (PORT B)

PC1

8

ACKB

PC2

INTE

B

PB7-PB0

OBFB

INTRB

PC0

WR

10

INTE

A

82C55A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IQ82C55AZ | IC I/O EXPANDER 24B 44MQFP |

| IMQ82C55AZ | IC I/O EXPANDER 24B 44MQFP |

| IMS82C55AZ96 | IC I/O EXPANDER 24B 44PLCC |

| IMS82C55AZ | IC I/O EXPANDER 24B 44PLCC |

| ATMEGA8535L-8JUR | MCU AVR 8K FLASH 8MHZ 44PLCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IQ83C151C-12 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ83C151C-16 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ83C151C-20 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ83C151C-25 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

| IQ83C151C-30 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。