- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378628 > IN74ACT74D (INTEGRAL JOINT STOCK COMPANY) DUAL D FLIP-FLOP WITH SET AND RESET PDF資料下載

參數(shù)資料

| 型號: | IN74ACT74D |

| 廠商: | INTEGRAL JOINT STOCK COMPANY |

| 英文描述: | DUAL D FLIP-FLOP WITH SET AND RESET |

| 中文描述: | 雙D觸發(fā)器與SET和RESET |

| 文件頁數(shù): | 1/5頁 |

| 文件大小: | 205K |

| 代理商: | IN74ACT74D |

IN74ACT74

1

D

UAL

D

F

LIP

-F

LOP WITH

S

ET AND

R

ESET

High-Speed Silicon-Gate CMOS

The IN74ACT74 is identical in pinout to the LS/ALS74,

HC/HCT74. The IN74ACT74 may be used as a level converter

for interfacing TTL or NMOS outputs to High Speed CMOS

inputs.

This device consists of two D flip-flops with individual Set,

Reset, and Clock inputs. Information at a D-input is transferred to

the corresponding Q output on the next positive going edge of

the clock input. Both Q and Q outputs are available from each

flip-flop. The Set and Reset inputs are asynchronous.

TTL/NMOS Compatible Input Levels

Outputs Directly Interface to CMOS, NMOS, and TTL

Operating Voltage Range: 4.5 to 5.5 V

Low Input Current: 1.0

μ

A; 0.1

μ

A @ 25

°

C

Outputs Source/Sink 24 mA

ORDERING INFORMATION

IN74ACT74N Plastic

IN74ACT74D SOIC

T

A

= -40

°

to 85

°

C for all

packages

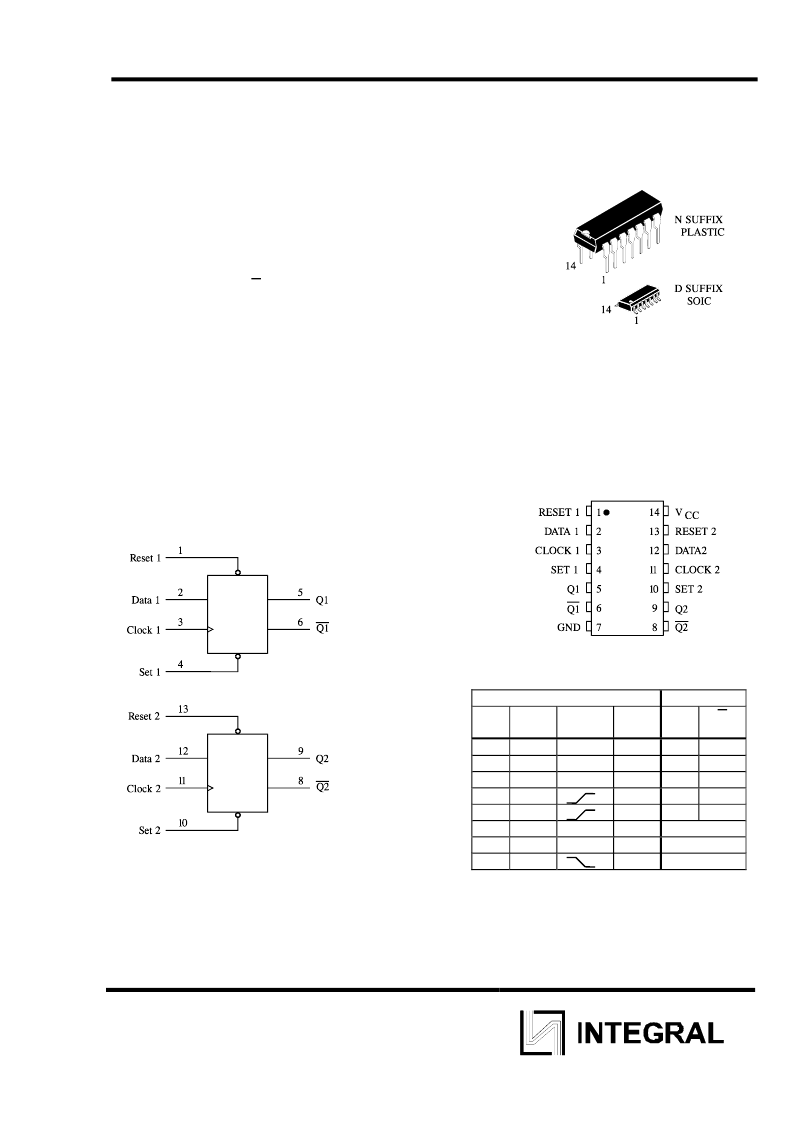

LOGIC DIAGRAM

PIN 14 =V

CC

PIN 7 = GND

PIN ASSIGNMENT

FUNCTION TABLE

Inputs

Rese

t

H

X

L

X

L

X

H

H

H

L

H

H

H

*Both outputs will remain high as long as Set

and Reset are low, but the output states are

unpredictable if Set and Reset go high

simultaneously.

X = don’t care

Outputs

Q

Set

Clock

Data

Q

L

H

L

H

H

H

H

H

X

X

X

H

L

X

X

X

H

L

H

*

H

L

No Change

No Change

No Change

L

H

H

*

L

H

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IN74ACT74N | DUAL D FLIP-FLOP WITH SET AND RESET |

| IN74ACT74 | DUAL D FLIP-FLOP WITH SET AND RESET |

| IN74ACT86 | Quad 2-Input Exclusive OR Gate |

| IN74ACT86D | Quad 2-Input Exclusive OR Gate |

| IN74ACT86N | Quad 2-Input Exclusive OR Gate |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IN74ACT74N | 制造商:INTEGRAL 制造商全稱:INTEGRAL 功能描述:DUAL D FLIP-FLOP WITH SET AND RESET |

| IN74ACT86 | 制造商:INTEGRAL 制造商全稱:INTEGRAL 功能描述:Quad 2-Input Exclusive OR Gate |

| IN74ACT86D | 制造商:INTEGRAL 制造商全稱:INTEGRAL 功能描述:Quad 2-Input Exclusive OR Gate |

| IN74ACT86N | 制造商:INTEGRAL 制造商全稱:INTEGRAL 功能描述:Quad 2-Input Exclusive OR Gate |

| IN74ALS240A | 制造商:INTEGRAL 制造商全稱:INTEGRAL 功能描述:OCTAL BUFFER / DRIVER WITH 3-STATE OUTPUTS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。