- 您現在的位置:買賣IC網 > PDF目錄360850 > IMIC9530 Clocks and Buffers PDF資料下載

參數資料

| 型號: | IMIC9530 |

| 英文描述: | Clocks and Buffers |

| 中文描述: | 時鐘和緩沖器 |

| 文件頁數: | 2/10頁 |

| 文件大小: | 125K |

| 代理商: | IMIC9530 |

C9530

Document #: 38-07033 Rev. *B

Page 2 of 10

Notes:

2.

Pin numbers ending with * indicate that they contain device internal pull-up resistors that will insure that they are sensed as a logic 1 if no external circuitry is

connected to them.

A bypass capacitor (0.1

μ

F) should be placed as close as possible to each V

DD

pin. If these bypass capacitors are not close to the pins their high-frequency

filtering characteristic will be cancelled by the lead inductance of the trace.

PWR = Power connection, I = Input, O = Output and I/O = both input and output functionality of the pin(s).

3.

4.

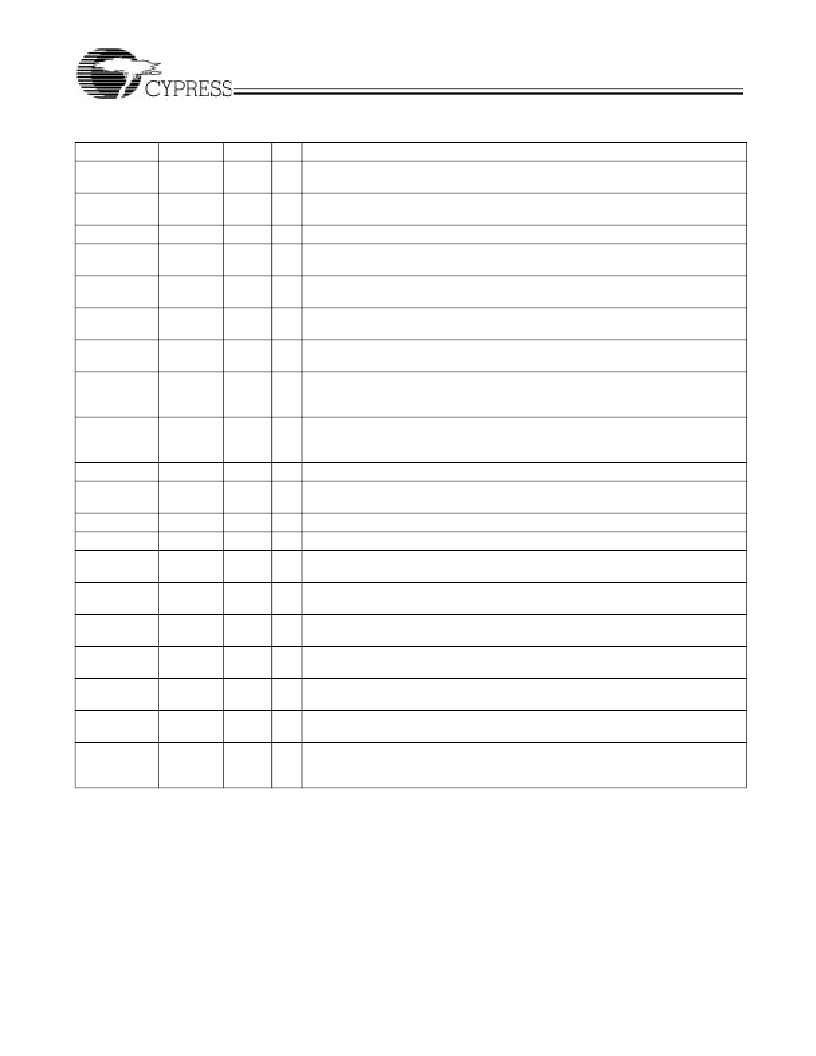

Pin Description

[3]

Pin

[2]

3

Name

XIN

PWR

[4]

VDDA

I/O

I

Description

Crystal Buffer input pin

. Connects to a crystal, or an external clock source. Serves

as input clock TCLK, in Test mode.

Crystal Buffer output pin

. Connects to a crystal only. When a Can Oscillator is used

or in Test mode, this pin is kept unconnected.

Buffered inverted outputs of the signal applied at Xin

, typically 33.33 or 25.0 MHz

Output Enable for clock bank A

. Causes the CLKA output clocks to be in a

three-state condition when driven to a logic low level.

Output Enable for clock bank B

. Causes the CLKB output clocks to be in a

three-state condition when driven to a logic low level.

When this output signal is a logic low level, it indicates that the

output clocks of the

A bank are locked to the input reference clock

. This output is latched.

When this output signal is at a logic low level, it indicates that the

output clocks of

the B bank are locked to the input reference clock

. This output is latched.

Clock Bank A selection bits

. These control the clock frequency that will be present

on the outputs of the A bank of buffers. See

Table 1

for frequency codes and selection

values.

Clock Bank B selection bits

. These control the clock frequency that will be present

on the outputs of the B bank of buffers. See

Table 1

for frequency codes and selection

values.

SMBus address selection input pins

. See

Table 3

SMBus Address table.

Enables Spread Spectrum clock modulation when at a logic low level, see

Spread

Spectrum Clocking

on page 6.

I/O

Data for the internal SMBus circuitry

.

I

Clock for the internal SMBus circuitry

.

PW

R

PW

R

PW

R

PW

R

decoupled current source from VDD.

O

A bank of five XINx1, XINx2, XINx3 and XINx4 output clocks

.

4

XOUT

VDDA

O

1

24*

REF

OEA

VDD

VDD

O

I

25*

OEB

VDD

I

18

AGOOD#

VDD

O

31

BGOOD#

VDD

O

6*, 7*

SA(0,1)

VDD

I

43*, 42*

SB(0,1)

VDD

I

20*, 21*, 22*

27*

IA(0:2)

SSCG#

VDD

VDD

I

I

48

47

11, 14

SDATA

SCLK

VDDA

VDD

VDD

–

3.3V common power supply pin for Bank A PCI clocks CLKA

.

38, 35

VDDB

–

3.3V common power supply pin for Bank B PCI clocks CLKB

.

2, 44, 46

VDD

–

Power supply for internal Core logic

.

23, 29, 30

AVDD

–

Power for internal analog circuitry

. This supply should have a separately

9, 10, 12, 15,

16

40, 39, 37, 34,

33

5, 8, 13, 17,

19, 26, 28, 32,

36, 41, 45

CLKA (0:4) VDDA

CLKB (0:4) VDDB

O

A bank of five XINx1, XINx2, XINx3 and XINx4 output clocks

.

VSS

–

PWR

Ground pins for the device

.

相關PDF資料 |

PDF描述 |

|---|---|

| IMIC9531 | Clocks and Buffers |

| IMIC9630 | Clocks and Buffers |

| IMIC9827H | Clocks and Buffers |

| IMIC9850A | Clocks and Buffers |

| IMIC9870G | Clocks and Buffers |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IMIC9530CT | 制造商:Cypress Semiconductor 功能描述: |

| IMIC9530CTT | 制造商:Cypress Semiconductor 功能描述: |

| IMIC9530CY | 制造商:Cypress Semiconductor 功能描述:Clock Generator 48-Pin SSOP |

| IMIC9530CYT | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:PCIX I/O System Clock Generator with EMI Control Features |

| IMIC9531 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Clocks and Buffers |

發(fā)布緊急采購,3分鐘左右您將得到回復。