- 您現在的位置:買賣IC網 > PDF目錄377485 > IDT7M1001S50CB (INTEGRATED DEVICE TECHNOLOGY INC) 128K x 8 64K x 8 CMOS DUAL-PORT STATIC RAM MODULE PDF資料下載

參數資料

| 型號: | IDT7M1001S50CB |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | 128K x 8 64K x 8 CMOS DUAL-PORT STATIC RAM MODULE |

| 中文描述: | 128K X 8 MULTI-PORT DEVICE SRAM MODULE, 50 ns, DMA64 |

| 文件頁數: | 5/11頁 |

| 文件大?。?/td> | 171K |

| 代理商: | IDT7M1001S50CB |

IDT7M1001/1003

128K/64K x 8 CMOS DUAL-PORT STATIC RAM MODULE

MILITARY AND COMMERCIAL TEMPERATURE RANGES

7.5

5

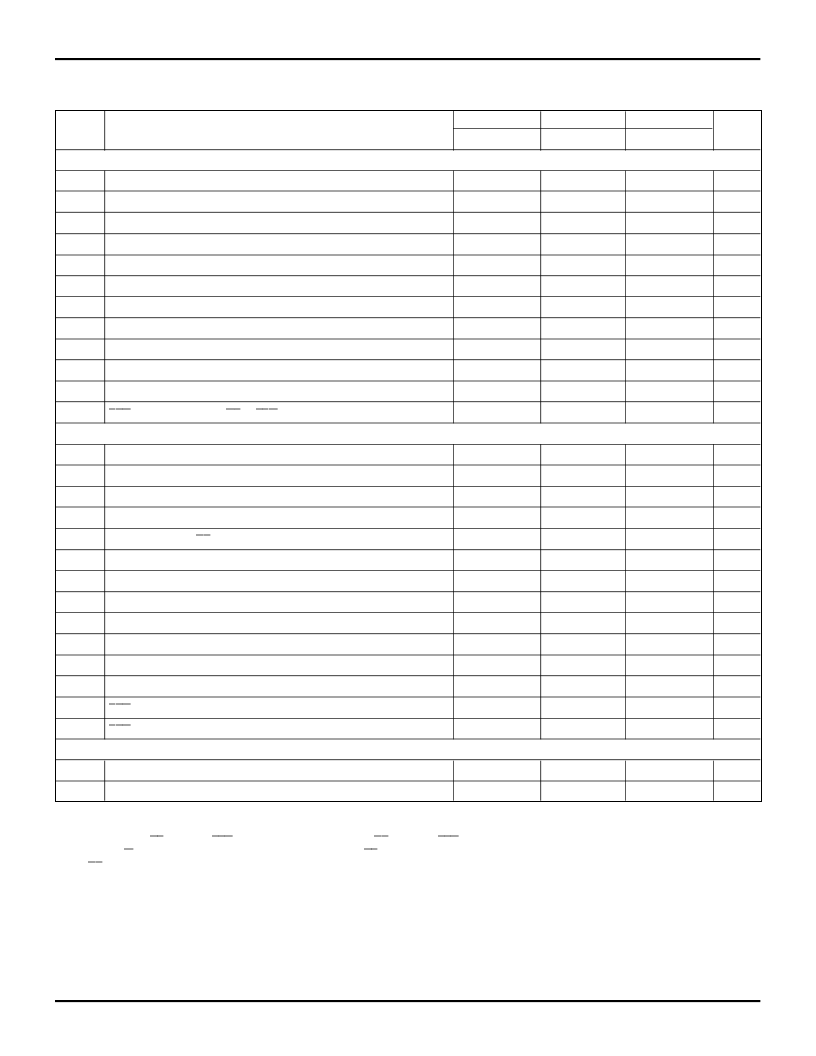

AC ELECTRICAL CHARACTERISTICS

(V

CC

= 5.0V

±

10%, T

A

= -55

°

C to +125

°

C and

0

°

C to +70

°

C)

–35

–40

–50

Symbol Parameter

Min.

Max.

Min.

Max.

Min.

Max.

Unit

Read Cycle

t

RC

Read Cycle Time

35

—

40

—

50

—

ns

t

AA

Address Access Time

—

35

—

40

—

50

ns

t

ACS

(2)

Chip Select Access Time

—

35

—

40

—

50

ns

t

OE

Output Enable Access Time

—

20

—

25

—

30

ns

t

OH

Output Hold From Address Change

3

—

3

—

3

—

ns

t

CLZ

(1)

Chip Select to Output in Low-Z

3

—

3

—

3

—

ns

t

CHZ

(1)

Chip Deselect to Output in High-Z

—

20

—

20

—

25

ns

t

OLZ

(1)

Output Enable to Output in Low-Z

3

—

3

—

3

—

ns

t

OHZ

(1)

Output Disable to Output in High-Z

—

20

—

20

—

25

ns

t

PU

(1)

Chip Select to Power-Up Time

0

—

0

—

0

—

ns

t

PD

(1)

Chip Disable to Power-Down Time

—

50

—

50

—

50

ns

t

SOP

SEM

Flag Update Pulse (

OE

or

SEM

)

15

—

15

—

15

—

ns

Write Cycle

t

WC

Write Cycle Time

35

—

40

—

50

—

ns

t

CW

(2)

Chip Select to End-of-Write

30

—

35

—

40

—

ns

t

AW

Address Valid to End-of-Write

30

—

35

—

40

—

ns

t

AS1

(3)

Address Set-up to Write Pulse Time

5

—

5

—

5

—

ns

t

AS2

Address Set-up to

CS

Time

0

—

0

—

0

—

ns

t

WP

Write Pulse Width

30

—

35

—

40

—

ns

t

WR

(4)

Write Recovery Time

0

—

0

—

0

—

ns

t

DW

Data Valid to End-of-Write

25

—

30

—

35

—

ns

t

DH

(4)

Data Hold Time

0

—

0

—

0

—

ns

t

OHZ

(1)

Output Disable to Output in High-Z

—

20

—

20

—

25

ns

t

WHZ

(1)

Write Enable to Output in High-Z

—

20

—

20

—

25

ns

t

OW

(1, 4)

Output Active from End-of-Write

0

—

0

—

0

—

ns

t

SWRD

SEM

Flag Write to Read Time

15

—

15

—

15

—

ns

t

SPS

SEM

Flag Contention Window

15

—

15

—

15

—

ns

Port-to-Port Delay Timing

t

WDD

(5)

Write Pulse to Data Delay

—

60

—

65

—

70

ns

t

DDD

(5)

Write Data Valid to Read Data Valid

—

45

—

50

—

55

ns

NOTES:

1. This parameter is guaranteed by design but not tested.

2. To access RAM

CS

≤

V

IL

and

SEM

≥

V

IH

. To access semaphore,

CS

≥

V

IH

and

SEM

≤

V

IL

.

3. t

AS1

= 0 if R/

W

is asserted LOW simultaneously with or after the

CS

LOW transition.

4. For

CS

controlled write cycles, t

WR

= 5ns, t

DH

= 5ns, t

OW

= 5ns.

5. Port-to-Port delay through the RAM cells from the writing port to the reading port.

2804 tbl 09

相關PDF資料 |

PDF描述 |

|---|---|

| IDT7M1003 | 128K x 8 64K x 8 CMOS DUAL-PORT STATIC RAM MODULE |

| IDT7M1003S35C | 128K x 8 64K x 8 CMOS DUAL-PORT STATIC RAM MODULE |

| IDT7M1003S35CB | 128K x 8 64K x 8 CMOS DUAL-PORT STATIC RAM MODULE |

| IDT7M1003S40C | 128K x 8 64K x 8 CMOS DUAL-PORT STATIC RAM MODULE |

| IDT7M1003S40CB | 128K x 8 64K x 8 CMOS DUAL-PORT STATIC RAM MODULE |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDT7M134S45C | 制造商:IDT 功能描述:IDT7M134S45C |

| IDT7M135S45C | 制造商:IDT 功能描述:IDT7M135S45C |

| IDT7M464S65C | 制造商:Integrated Device Technology Inc 功能描述:Static RAM Memory Module, 16K x 4, 22 Pin, Ceramic, DIP |

| IDT7M464S85C | 制造商:Integrated Device Technology Inc 功能描述:Static RAM Memory Module, 16K x 4, 22 Pin, Ceramic, DIP |

| IDT7M624S45CB | 制造商:Integrated Device Technology Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。