- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4018 > IDT79RC64V475-180DP (IDT, Integrated Device Technology Inc)IC MPU 64BIT EMB 180MHZ 208-QFP PDF資料下載

參數(shù)資料

| 型號: | IDT79RC64V475-180DP |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 20/25頁 |

| 文件大小: | 0K |

| 描述: | IC MPU 64BIT EMB 180MHZ 208-QFP |

| 標準包裝: | 24 |

| 處理器類型: | RISC 64-位 |

| 速度: | 180MHz |

| 電壓: | 3.3V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 208-BFQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 包裝: | 托盤 |

| 其它名稱: | 79RC64V475-180DP |

4 of 25

April 10, 2001

RC64474 RC64475

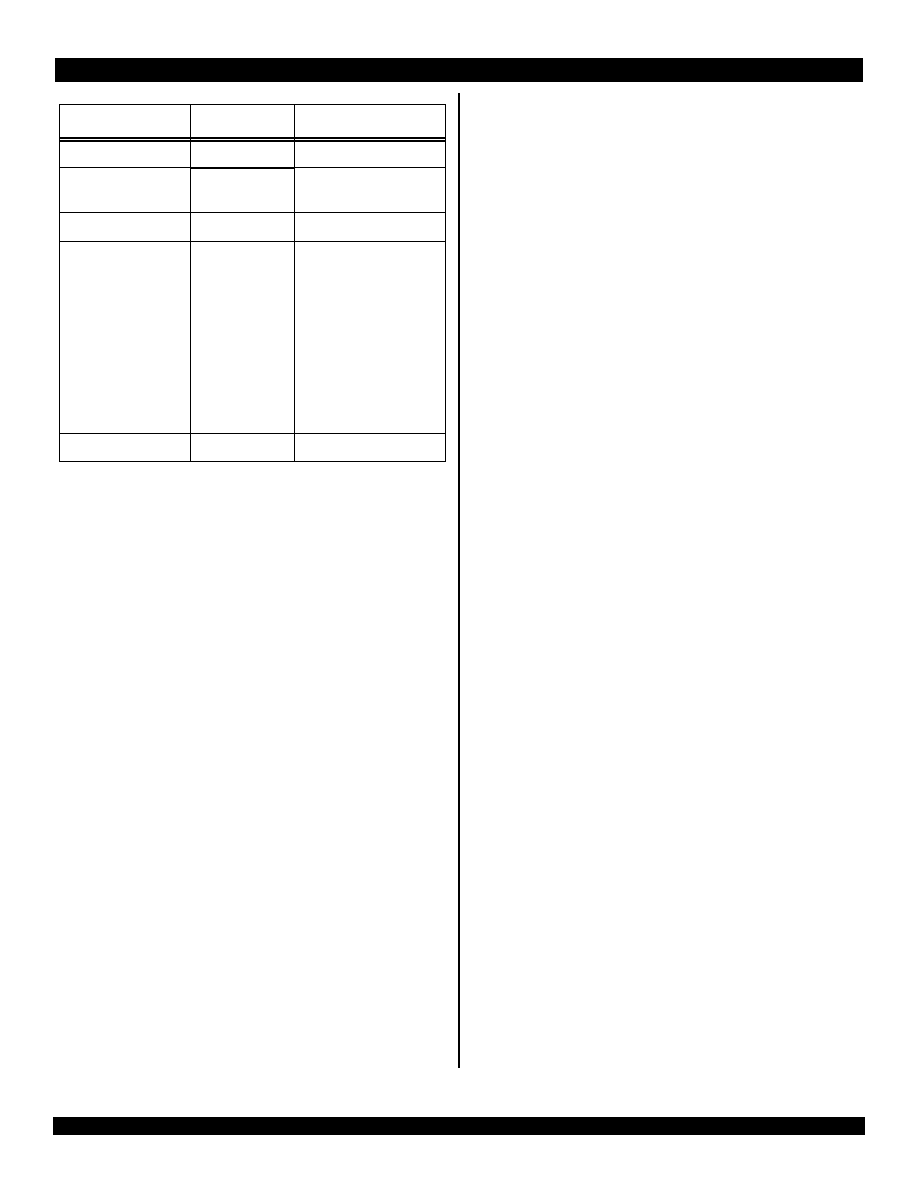

Table 2 RC64474/RC64475 Instruction/Data Cache Attributes

System Interfaces

The RC64475 supports a 64-bit system interface that is bus compat-

ible with the RC4650 and RC64575 system interface. The system inter-

face consists of a 64-bit Address/Data bus with 8 check bits and a 9-bit

command bus that is parity protected.

During 64-bit operation, RC64475 system address/data (SysAD)

transfers are protected with an 8-bit parity check bus, SysADC. When

initialized for 32-bit operation, the RC64475’s SysAD can be viewed as a

32-bit multiplexed bus that is protected by 4 parity check bits.

The RC64474 supports a 32-bit system interface that is bus compat-

ible with the RC4640. During 32-bit operation, SysAD transfers are

performed on a 32-bit multiplexed bus (SysAD 31:0) that is protected by

4 parity check bits (SysADC 6:0).

Writes to external memory—whether they are cache miss write-

backs, stores to uncached or write-through addresses—use the on-chip

write buffer. The write buffer holds a maximum of four 64-bit addresses

and 64-bit data pairs. The entire buffer is used for a data cache write-

back and allows the processor to proceed in parallel with memory

updates.

Included in the system interface are six handshake signals:

RdRdy*, WrRdy*, ExtRqst*, Release*, ValidOut*, and ValidIn*; six inter-

rupt inputs, and a simple timing specification that is capable of trans-

ferring data between the processor and memory at a peak rate of

1000MB/sec. A boot-time selectable option to run the system interface

as 32-bits wide—using basically the same protocols as the 64-bit

system—is also supported.

Characteristics

Instruction

Data

Size

16KB

Organization

2-way set

associative

2-way set

associative

Line size

32B

read unit

32-bits

64-bits

write policy

na

write-back, write-through

with or without write-allocate

Line transfer order

sub-block order,

for refill

sub-block order, for load

sequential order, for store

Miss restart

after transfer of:

entire line

miss word

Parity

per-word

per-byte

Cache locking

per set

A boot-time mode control interface initializes fundamental

processor modes. The boot-time mode control interface is a serial inter-

face that operates at a very low frequency (MasterClock divided by

256). This low-frequency operation allows the initialization information to

be kept in a low-cost EPROM; alternatively, the twenty-or-so bits could

be generated by the system interface ASIC or a simple PAL. The boot-

time serial stream and configuration options are listed in Table 3.

The clocking interface allows the CPU to be easily mated with

external reference clocks. The CPU input clock is the bus reference

clock and can be between 25 and 125MHz. An on-chip phase-locked-

loop (PLL) generates the pipeline clock (PClock) through multiplication

of the system interface clock by values of 2,3,4,5,6,7 or 8, as defined at

system reset. This allows the pipeline clock to be implemented at a

significantly higher frequency than the system interface clock. The

RC64474/475 support single data (one to eight bytes) and 8-word block

transfers on the SysAD bus.

The RC64474/475 implement additional write protocols that

double the effective write bandwidth. The write re-issue has a repeat

rate of 2 cycles per write. Pipelined writes have the same 2-cycle per

write repeat rate, but can issue an additional write after WrRdy* de-

asserts.

Choosing a 32- or 64-bit wide system interface dictates whether a

cache line block transaction requires 4 double word data cycles or 8

single word cycles as well as whether a single data transfer—larger than

4 bytes—must be divided into two smaller transfers.

Board-level testing during Run-Time mode is facilitated through the

full JTAG boundary scan facility. Six pins—TDI, TDO, TMS, TCK, TRST*

and JTAG32*—have been incorporated to support the standard JTAG

interface.

System Enhancement

To facilitate discrete interface to SDRAM, the RC64474/475 bus

interface is enhanced during write cycles with a programmable delay

that is inserted between the write address and the write data (for both

block and non-block writes).

The bus delay can be defined as 0 to 7 MasterClock cycles and is

activated and controlled through mode bit (17:15) settings selected

during the reset initialization sequence. The ‘000’ setting provides the

same write operations timing protocol as the RC4640, RC4650, and

RC5000 processors.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMM44DRKI-S13 | CONN EDGECARD 88POS .156 EXTEND |

| AMC65DRYI-S13 | CONN EDGECARD 130POS .100 EXTEND |

| IDT79RC64V474-200DZ | IC MPU 64BIT EMB 200MHZ 128-QFP |

| GMC40DTES | CONN EDGECARD 80POS .100 EYELET |

| EMC40DTEI | CONN EDGECARD 80POS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT79RC64V475-200DP | 功能描述:IC MPU 64BIT EMB 200MHZ 208-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標準包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RV4640-133DU | 功能描述:IC SGL BOARD COMPUTER 128-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標準包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RV4640-133DUG | 功能描述:IC SGL BOARD COMPUTER 128-QFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標準包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RV4640-150DU | 功能描述:IC SGL BOARD COMPUTER 128-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標準包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RV4640-150DUG | 功能描述:IC SGL BOARD COMPUTER 128-QFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標準包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。