- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4019 > IDT79RC32V332-133DHG (IDT, Integrated Device Technology Inc)IC PROC 32BIT CPU 133MHZ 208-QFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT79RC32V332-133DHG |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 2/30頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC PROC 32BIT CPU 133MHZ 208-QFP |

| 產(chǎn)品變化通告: | Product Discontinuation 07/Dec/2009 |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | Interprise™ |

| 處理器類型: | RISC 32-位 |

| 速度: | 133MHz |

| 電壓: | 3.3V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 包裝: | 托盤 |

| 其它名稱: | 79RC32V332-133DHG |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)

10 of 30

May 4, 2004

IDT 79RC32332

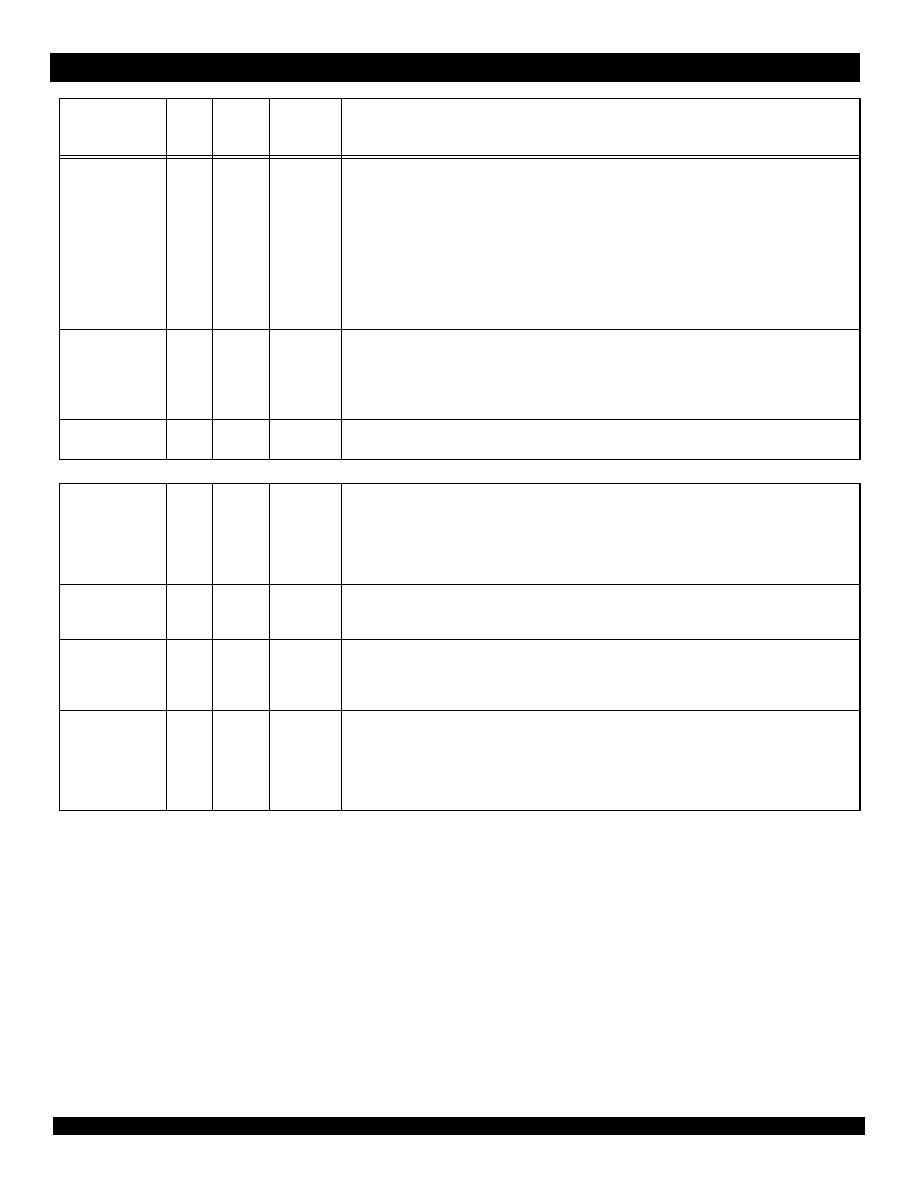

ejtag_pcst[2:0]

I/O

Z

Low

EJTAG PC Trace Status Information

111 (STL) Pipe line Stall

110 (JMP) Branch/Jump forms with PC output

101 (BRT) Branch/Jump forms with no PC output

100 (EXP) Exception generated with an exception vector code output

011 (SEQ) Sequential performance

010 (TST) Trace is outputted at pipeline stall time

001 (TSQ) Trace trigger output at performance time

000 (DBM) Run Debug Mode

Alternate function: modebit[2:0].

ejtag_debugboot

Input

—

EJTAG DebugBoot Requires an external pull-down.

The ejtag_debugboot input is used during reset and forces the CPU core to take a debug exception at the

end of the reset sequence instead of a reset exception. This enables the CPU to boot from the ICE probe

without having the external memory working. This input signal is level sensitive and is not latched inter-

nally. This signal will also set the JtagBrk bit in the JTAG_Control_Register[12].

ejtag_tms

Input

—

EJTAG Test Mode Select Requires an external pull-up.

The ejtag_tms is sampled on the rising edge of jtag_tck.

Debug Signals

debug_cpu_dma_n

I/O

Z

Low

Debug CPU versus DMA Negated

De-assertion high during debug_cpu_ads_n assertion or debug_cpu_ack_n assertion indicates transac-

tion was generated from the CPU.

Assertion low during debug_cpu_ads_n assertion or debug_cpu_ack_n assertion indicates transaction

was generated from DMA.

Alternate function: modebit[6].

debug_cpu_ack_n

I/O

Z

Low

Debug CPU Acknowledge Negated

Indicates either a data acknowledge to the CPU or DMA.

Alternate function: modebit[4].

debug_cpu_ads_n

I/O

Z

Low

Debug CPU Address/Data Strobe Negated

Assertion indicates that either a CPU or a DMA transaction is beginning and that the mem_data[31:4] bus

has the current block address.

Alternate function: modebit[5].

debug_cpu_i_d_n

I/O

Z

Low

Debug CPU Instruction versus Data Negated

Assertion during debug_cpu_ads_n assertion or debug_cpu_ack_n assertion indicates transaction is a

CPU or DMA data transaction.

De-assertion during debug_cpu_ads_n assertion or debug_cpu_ack_n assertion indicates transaction is

a CPU instruction transaction.

Alternate function: modebit[3].

Name

Type

Reset

State

Status

Drive

Strength

Capability

Description

Table 1 Pin Descriptions (Part 6 of 6)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT70V35S15PF | IC SRAM 144KBIT 15NS 100TQFP |

| IDT709149S10PF8 | IC SRAM 36KBIT 10NS 80TQFP |

| FMM43DSEI | CONN EDGECARD 86POS .156 EYELET |

| FMM43DRKI | CONN EDGECARD 86POS DIP .156 SLD |

| EMC31DTEF | CONN EDGECARD 62POS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT79RC32V332-133DHGI | 制造商:Integrated Device Technology Inc 功能描述:IC PROC 32BIT CPU 133MHZ 208-QFP |

| IDT79RC32V332-133DHI | 功能描述:IC PROC 32BIT CPU 133MHZ 208-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:Interprise™ 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點(diǎn):- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RC32V332-150DH | 功能描述:IC PROC 32BIT CPU 150MHZ 208-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:Interprise™ 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點(diǎn):- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RC32V332-150DHG | 功能描述:IC PROC 32BIT CPU 150MHZ 208-QFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:Interprise™ 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點(diǎn):- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RC32V333-100DH | 功能描述:IC PROC 32BIT CPU 100MHZ 208-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:Interprise™ 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點(diǎn):- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。