- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9989 > IDT72V3656L10PF8 (IDT, Integrated Device Technology Inc)IC SYNC FIFO 4096X36 10NS 128QFP PDF資料下載

參數(shù)資料

| 型號: | IDT72V3656L10PF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 26/39頁 |

| 文件大小: | 0K |

| 描述: | IC SYNC FIFO 4096X36 10NS 128QFP |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 系列: | 72V |

| 功能: | 異步 |

| 存儲容量: | 147K(4K x 36) |

| 數(shù)據(jù)速率: | 100MHz |

| 訪問時間: | 10ns |

| 電源電壓: | 3.15 V ~ 3.45 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 128-LQFP |

| 供應(yīng)商設(shè)備封裝: | 128-TQFP(14x20) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72V3656L10PF8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

32

COMMERCIALTEMPERATURERANGE

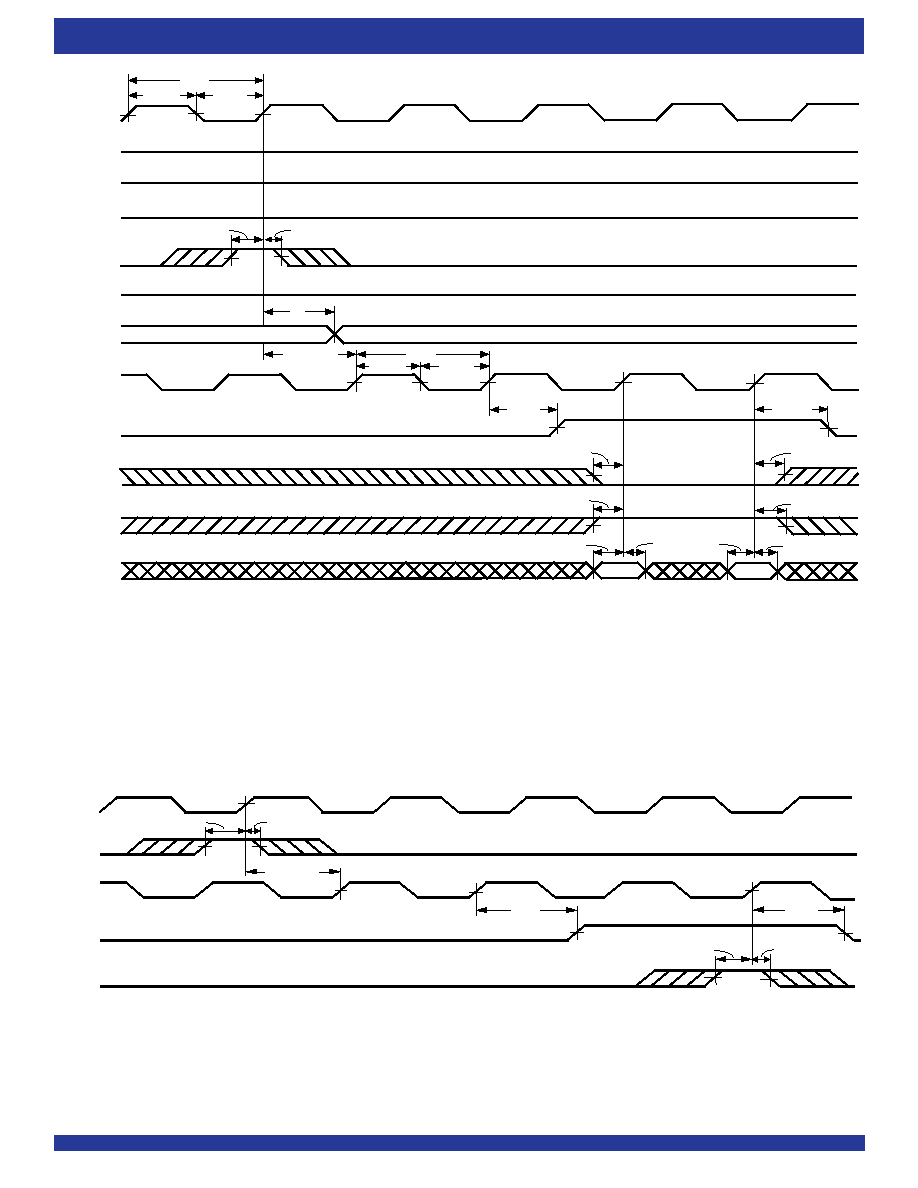

IDT72V3656/72V3666/72V3676 3.3V CMOS TRIPLE BUS SyncFIFOTM

WITH BUS MATCHING 2,048 x 36 x 2, 4,096 x 36 x 2 and 8,192 x 36 x 2

NOTES:

1. tSKEW2 is the minimum time between a rising CLKA edge and a rising CLKB edge for

AEB to transition HIGH in the next CLKB cycle. If the time between the rising CLKA edge and rising

CLKB edge is less than tSKEW2, then

AEB may transition HIGH one CLKB cycle later than shown.

2. FIFO1 Write (

CSA = LOW, W/RA = LOW, MBA = LOW), FIFO1 read (CSB = LOW, MBB = LOW). Data in the FIFO1 output register has been read from the FIFO.

3. If Port B size is word or byte,

AEB is set LOW by the last word or byte read from FIFO1, respectively.

Figure 24. Timing for

AEB

AEB when FIFO1 is Almost-Empty (IDT Standard and FWFT Modes)

Figure 23.

FFC

FFC Flag Timing and First Available Write when FIFO2 is Full (IDT Standard Mode)

NOTES:

1. tSKEW1 is the minimum time between a rising CLKA edge and a rising CLKC edge for

FFC to transition HIGH in the next CLKC cycle. If the time between the rising CLKA edge and rising

CLKC edge is less than tSKEW1, then

FFC may transition HIGH one CLKC cycle later than shown.

2. If Port C size is word or byte,

FFC is set LOW by the last word or byte write of the long word, respectively (the word-size case is shown).

CSA

EFA

MBA

ENA

A0-A35

CLKA

FFC

CLKC

4665 drw24

12

C0-C17

MBC

ENC

tCLK

tCLKH

tCLKL

tENS2

tENH

tA

tSKEW1

tCLK

tCLKH

tCLKL

tENS2

tDS

tENH

tDH

To FIFO2

Previous Word in FIFO2 Output Register

Next Word From FIFO2

LOW

W/RA

LOW

HIGH

(1)

FIFO2 Full

tWFF

tDH

tDS

Write

AEB

CLKA

RENB

4665 drw 25

ENA

CLKB

2

1

tENS2

tENH

tSKEW2

tPAE

tENS2

tENH

X1 Word in FIFO1

(X1+1) Words in FIFO1

(1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-BNF-IV-F2 | CONVERTER MOD DC/DC 72V 150W |

| IDT72V3654L10PF8 | IC BI FIFO 4096X36 10NS 128QFP |

| VI-BNF-IV-F1 | CONVERTER MOD DC/DC 72V 150W |

| IDT72V3653L10PF8 | IC SYNCFIFO 2048X36 10NS 128TQFP |

| VI-BND-IV-F4 | CONVERTER MOD DC/DC 85V 150W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V3656L10PFI | 制造商:Integrated Device Technology Inc 功能描述:IC SYNC FIFO 4096X36 10NS 128QFP |

| IDT72V3656L10PFI8 | 制造商:Integrated Device Technology Inc 功能描述:IC SYNC FIFO 4096X36 10NS 128QFP |

| IDT72V3656L15PF | 功能描述:IC SYNC FIFO 4096X36 15NS 128QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3656L15PF8 | 功能描述:IC SYNC FIFO 4096X36 15NS 128QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3660L10PF | 功能描述:IC FIFO SS 4096X36 10NS 128-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。