- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377424 > IDT72831L10TF (INTEGRATED DEVICE TECHNOLOGY INC) DUAL CMOS SyncFIFO PDF資料下載

參數(shù)資料

| 型號: | IDT72831L10TF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | DUAL CMOS SyncFIFO |

| 中文描述: | 2K X 9 BI-DIRECTIONAL FIFO, 6.5 ns, PQFP64 |

| 封裝: | SLIM, TQFP-64 |

| 文件頁數(shù): | 12/16頁 |

| 文件大小: | 169K |

| 代理商: | IDT72831L10TF |

12

Commercial And Industrial Temperature Range

IDT72801/728211/72821/72831/72841/72851

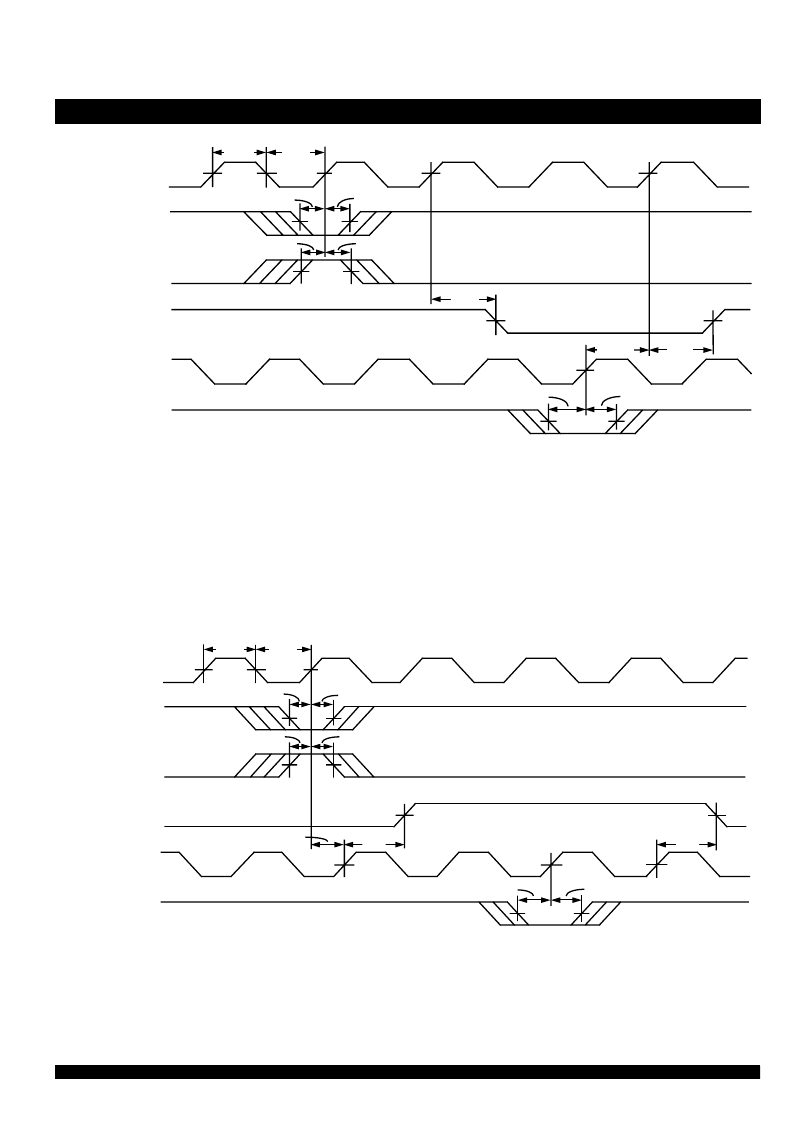

Figure 10. Programmable Full Flag Timing

NOTES:

1. m=

PAF

offset.

2. (256-m words for the IDT72801; (512-m words the IDT72811; (1,024-m words for the IDT72821; (2,048-m words for the IDT72831; (4,096-m words for the IDT72841; or (8,192-m

words for the IDT72851.

3. t

SKEW2

is the mnimumtime between a rising RCLKA (RCLKB) edge and a rising WCLKA (WCLKB) edge for

PAFA

(

PAFB

) to change during that clock cycle. If the time between the

rising edge of RCLKA (RCLKB) and the rising edge of WCLKA (WCLKB) is less than t

SKEW2

, then

PAFA

(

PAFB

) may not change state until the next WCLKA (WCLKB) rising edge.

4. If a write is performed on this rising edge of the write clock, there will be Full - (m-1) words in FIFO A (B) when

PAFA

(

PAFB

) goes LOW.

t

ENS

t

ENH

t

ENS

t

ENH

t

ENS

t

ENH

WCLKA

(WCLKB)

WENA1

(

WENB1

)

WENA2 (WENB2)

(If Applicable)

PAFA

(

PAFB

)

RCLKA (RCLKB)

RENA1

,

RENA2

(

RENB1

,

RENB2

)

(4)

(1)

t

PAF

Full - (m+1) words in FIFO

Full - m words in FIFO

(2)

t

CLKH

t

CLKL

t

SKEW2

(3)

t

PAF

3034 drw 11

WCLKA (WCLKB)

WENA1

(

WENB1

)

WENA2 (WENB2)

(If Applicable)

PAEA

,

PAEB

RCLKA (RCLKB)

RENA1

,

RENA2

(

RENB1

,

RENB2

)

t

ENS

t

ENH

t

ENS

t

ENH

t

SKEW2(2)

t

ENS

t

ENH

t

PAE

t

PAE

(3)

(1)

n words in FIFO

n+1 words in FIFO

t

CLKH

t

CLKL

3034 drw 12

NOTES:

1.

2.

n =

PAE

offset.

t

SKEW2

is the mnimumtime between a rising WCLKA (WCLKB) edge and a rising RCLKA (RCLKB) edge for

PAEA

(

PAEB

) to change during that clock cycle. If the time between the

rising edge of WCLKA (WCLKB) and the rising edge of RCLKA (RCLKB) is less than t

SKEW2

, then

PAEA

(

PAEB

) may not change state until the next RCLKA (RCLKB) rising edge.

If a read is performed on this rising edge of the read clock, there will be Empty + (n-1) words in FIFO A (B) when

PAEA

(

PAEB

) goes LOW.

3.

Figure 11. Programmable Empty Flag Timing

相關PDF資料 |

PDF描述 |

|---|---|

| IDT72831L10TFI | DUAL CMOS SyncFIFO |

| IDT72831L15PFI | DUAL CMOS SyncFIFO |

| IDT72831L15TF | DUAL CMOS SyncFIFO |

| IDT72831L15TFI | DUAL CMOS SyncFIFO |

| IDT72831L25TF | DUAL CMOS SyncFIFO |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72831L10TF8 | 功能描述:IC FIFO SYNC DUAL 2048X9 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72831L15PF | 功能描述:IC FIFO SYNC DUAL 2048X9 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72831L15PF8 | 功能描述:IC FIFO SYNC DUAL 2048X9 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72831L15PFI | 功能描述:IC FIFO SYNC DUAL 2048X9 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72831L15PFI8 | 功能描述:IC FIFO SYNC DUAL 2048X9 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復。