- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377359 > IDT7201LA80D (INTEGRATED DEVICE TECHNOLOGY INC) CMOS ASYNCHRONOUS FIFO 256 x 9, 512 x 9, 1K x 9 PDF資料下載

參數(shù)資料

| 型號: | IDT7201LA80D |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | CMOS ASYNCHRONOUS FIFO 256 x 9, 512 x 9, 1K x 9 |

| 中文描述: | 512 X 9 OTHER FIFO, 80 ns, CDIP28 |

| 封裝: | 0.600 INCH, CERDIP-28 |

| 文件頁數(shù): | 5/14頁 |

| 文件大小: | 152K |

| 代理商: | IDT7201LA80D |

5.03

5

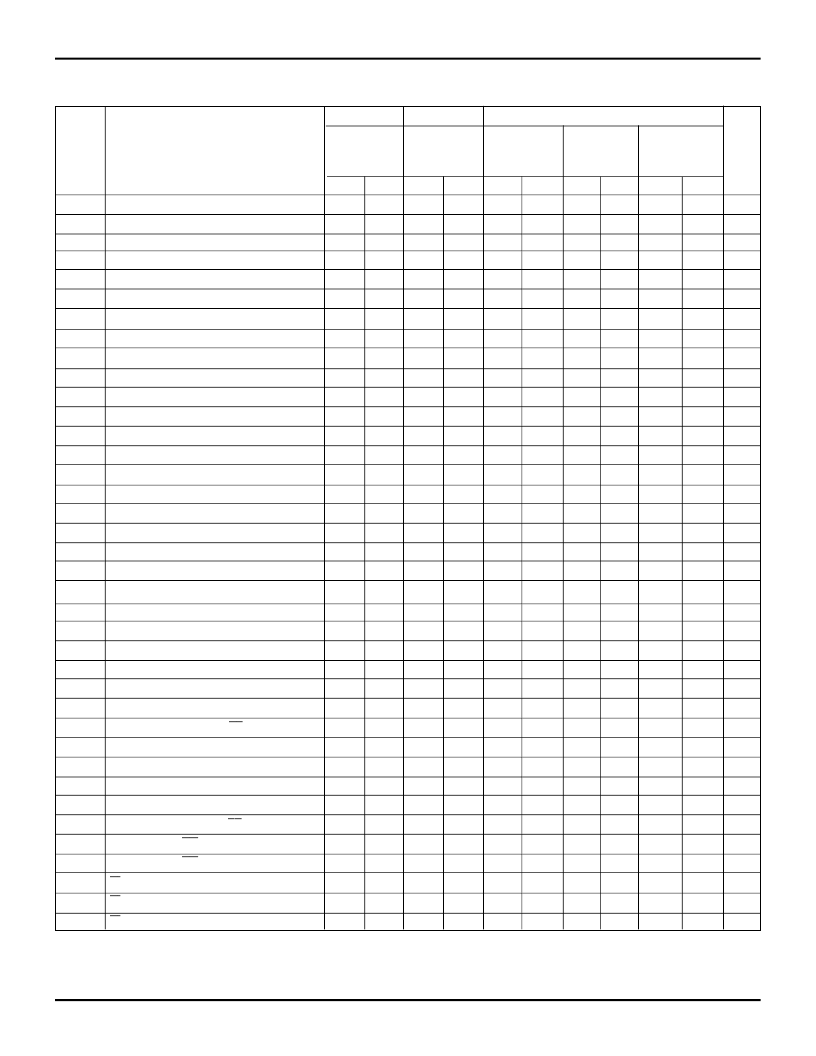

IDT7200/7201A/7202A CMOS ASYNCHRONOUS FIFO

256 x 9, 512 x 9 and 1K x 9

MILITARY AND COMMERCIAL TEMPERATURE RANGES

AC ELECTRICAL CHARACTERISTICS

(1)

(Continued)

(Commercial: V

CC

= 5.0V

±

10%, T

A

= 0

°

C to +70

°

C; Military: V

CC

= 5.0V

±

10%, T

A

= –55

°

C to +125

°

C)

Military

7200 L40

7201LA40

7202LA40

Min.

—

50

—

10

40

5

10

5

—

50

40

10

20

0

50

40

40

10

50

40

40

10

—

—

—

—

—

40

—

—

—

—

40

—

—

40

10

10

Com'l & Mil.

7200L50

7201LA50

7202LA50

Min.

—

65

—

15

50

10

15

5

—

65

50

15

30

5

65

50

50

15

65

50

50

15

—

—

—

—

—

50

—

—

—

—

50

—

—

50

10

15

Military

(2)

7200L80

7201LA80

7202LA80

Min.

—

100

—

20

80

10

20

5

—

100

80

20

40

10

100

80

80

20

100

80

80

20

—

—

—

—

—

80

—

—

—

—

80

—

—

80

10

15

7200L65

7201LA65

7202LA65

Min.

—

80

—

15

65

10

15

5

—

80

65

15

30

10

80

65

65

15

80

65

65

15

—

—

—

—

—

65

—

—

—

—

65

—

—

65

10

15

7200L120

7201LA120

7202LA120

Min.

—

140

—

20

120

10

20

5

—

140

120

20

40

10

140

120

120

20

140

120

120

20

—

—

—

—

—

120

—

—

—

—

120

—

—

120

10

15

Symbol

t

S

t

RC

t

A

t

RR

t

RPW

t

RLZ

t

WLZ

t

DV

t

RHZ

t

WC

t

WPW

t

WR

t

DS

t

DH

t

RSC

t

RS

t

RSS

t

RSR

t

RTC

t

RT

t

RTS

t

RTR

t

EFL

t

HFH,FFH

Reset to Half-Full and Full Flag High

t

RTF

Retransmit Low to Flags Valid

t

REF

Read Low to Empty Flag Low

t

RFF

Read High to Full Flag High

t

RPE

Read Pulse Width after

EF

High

t

WEF

Write High to Empty Flag High

t

WFF

Write Low to Full Flag Low

t

WHF

Write Low to Half-Full Flag Low

t

RHF

Read High to Half-Full Flag High

t

WPF

Write Pulse Width after

FF

High

t

XOL

Read/Write to

XO

Low

t

XOH

Read/Write to

XO

High

t

XI

XI

Pulse Width

(3)

t

XIR

XI

Recovery Time

t

XIS

XI

Set-up Time

Parameter

Max.

20

—

40

—

—

—

—

—

25

—

—

—

—

—

—

—

—

—

—

—

—

—

50

50

50

30

35

—

35

35

50

50

—

40

40

—

—

—

Max.

15

—

50

—

—

—

—

—

30

—

—

—

—

—

—

—

—

—

—

—

—

—

65

65

65

45

45

—

45

45

65

65

—

50

50

—

—

—

Max.

12.5

—

65

—

—

—

—

—

30

—

—

—

—

—

—

—

—

—

—

—

—

—

80

80

80

60

60

—

60

60

80

80

—

65

65

—

—

—

Max.

10

—

80

—

—

—

—

—

30

—

—

—

—

—

—

—

—

—

—

—

—

—

100

100

100

60

60

—

60

60

100

100

—

80

80

—

—

—

Max.

7

—

120

—

—

—

—

—

35

—

—

—

—

—

—

—

—

—

—

—

—

—

140

140

140

60

60

—

60

60

140

140

—

120

120

—

—

—

Unit

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Shift Frequency

Read Cycle Time

Access Time

Read Recovery Time

Read Pulse Width

(3)

Read Pulse Low to Data Bus at Low Z

(4)

Write Pulse High to Data Bus at Low Z

(4, 5)

Data Valid from Read Pulse High

Read Pulse High to Data Bus at High Z

(4)

Write Cycle Time

Write Pulse Width

(3)

Write Recovery Time

Data Set-up Time

Data Hold Time

Reset Cycle Time

Reset Pulse Width

(3)

Reset Set-up Time

(4)

Reset Recovery Time

Retransmit Cycle Time

Retransmit Pulse Width

(3)

Retransmit Set-up Time

(4)

Retransmit Recovery Time

Reset to Empty Flag Low

NOTES:

1. Timings referenced as in AC Test Conditions

2. Speed grades 65, 80 and 120 not available in the CERPACK

3. Pulse widths less than minimum value are not allowed.

2679 tbl 07

4. Values guaranteed by design, not currently tested.

5. Only applies to read data flow-through mode.

相關PDF資料 |

PDF描述 |

|---|---|

| IDT7201LA80J | CMOS ASYNCHRONOUS FIFO 256 x 9, 512 x 9, 1K x 9 |

| IDT7201LA80L | CMOS ASYNCHRONOUS FIFO 256 x 9, 512 x 9, 1K x 9 |

| IDT7201LA80P | CMOS ASYNCHRONOUS FIFO 256 x 9, 512 x 9, 1K x 9 |

| IDT7200LA20SOB | 20 Characters x 2 Lines, 5x7 Dot Matrix Character and Cursor |

| IDT7201LA20SOB | 20 Characters x 2 Lines, 5x7 Dot Matrix Character and Cursor |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IDT7201LA80DB | 制造商:Integrated Device Technology Inc 功能描述:IC MEM FIFO 512X9 ASYNC 28CDIP 制造商:Integrated Device Technology Inc 功能描述:FIFO, 512 x 9, Asynchronous, 28 Pin, Ceramic, DIP |

| IDT7201LA80J | 制造商:Integrated Device Technology Inc 功能描述:FIFO, 512 x 9, Asynchronous, 32 Pin, Plastic, PLCC |

| IDT7201LA80TDB | 制造商:Integrated Device Technology Inc 功能描述: 制造商:Integrated Device Technology Inc 功能描述:IC MEM FIFO 512X9 ASYNC 28CDIP 制造商:Integrated Device Technology Inc 功能描述:FIFO, 512 x 9, Asynchronous, 28 Pin, Ceramic, DIP |

| IDT7201S120CB | 制造商:Integrated Device Technology Inc 功能描述:FIFO, 512 x 9, Asynchronous, 28 Pin, Ceramic, DIP |

| IDT7201S120D | 制造商:Integrated Device Technology Inc 功能描述:FIFO, 512 x 9, Asynchronous, 28 Pin, Ceramic, DIP |

發(fā)布緊急采購,3分鐘左右您將得到回復。