- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377294 > IDT71256S35YB (Integrated Device Technology, Inc.) Replaced by TL16C550C : Single UART with 16-Byte FIFOs 44-PLCC 0 to 70 PDF資料下載

參數(shù)資料

| 型號(hào): | IDT71256S35YB |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | Replaced by TL16C550C : Single UART with 16-Byte FIFOs 44-PLCC 0 to 70 |

| 中文描述: | 的CMOS靜態(tài)RAM 256K(32K的× 8位) |

| 文件頁(yè)數(shù): | 7/9頁(yè) |

| 文件大小: | 78K |

| 代理商: | IDT71256S35YB |

7.2

7

IDT71256S/L

CMOS STATIC RAM 256K (32K x 8-BIT)

MILITARY AND COMMERCIAL TEMPERATURE RANGES

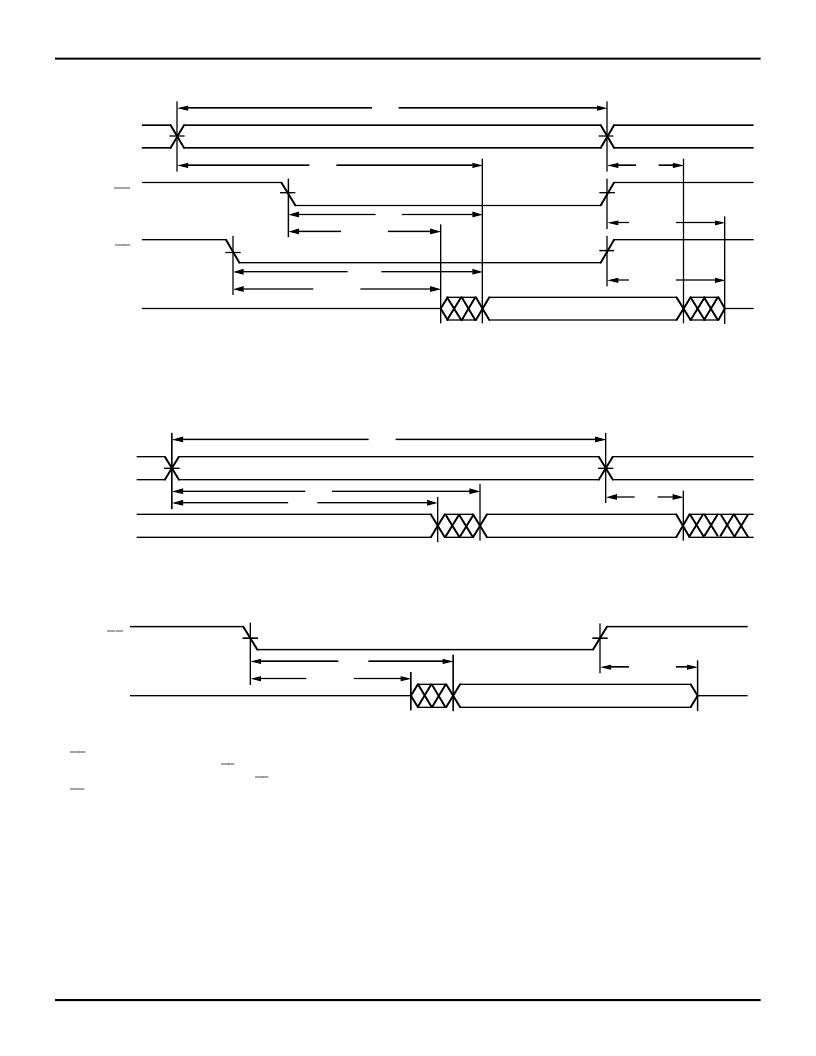

TIMING WAVEFORM OF READ CYCLE NO. 1

(1)

TIMING WAVEFORM OF READ CYCLE NO. 3

(1, 3, 4)

TIMING WAVEFORM OF READ CYCLE NO. 2

(1, 2, 4)

NOTES:

1.

WE

is HIGH for Read cycle.

2. Device is continuously selected,

CS

is LOW.

3. Address valid prior to or coincident with

CS

transition LOW.

4.

OE

is LOW.

5. Transition is measured

±

200mV from steady state.

2946 drw 07

ADDRESS

CS

DATA

OUT

t

RC

t

AA

t

OH

t

ACS

(5)

t

CLZ

t

CHZ(5)

t

OE

t

OLZ

(5)

t

OHZ(5)

OE

2946 drw 08

ADDRESS

t

RC

t

AA

t

OH

t

OH

DATA

OUT

2946 drw 09

DATA

OUT

CS

t

ACS

(5)

t

CLZ

(5)

t

CHZ

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT71256S45D | Replaced by TL16C550C : Single UART with 16-Byte FIFOs 44-PLCC -40 to 85 |

| IDT71256S45DB | Replaced by TL16C550C : Single UART with 16-Byte FIFOs 48-LQFP -40 to 85 |

| IDT71256S45L | Replaced by TL16C550C : Single UART with 16-Byte FIFOs 40-PDIP 0 to 70 |

| IDT71256S45LB | Replaced by TL16C550C : Single UART with 16-Byte FIFOs 48-LQFP 0 to 70 |

| IDT71256S45P | CMOS STATIC RAM 256K (32K x 8-BIT) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT71256S45DB | 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 256KBIT 45NS 28CDIP |

| IDT71256S45TDB | 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 256KBIT 28CDIP |

| Idt71256S55DB | 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 256KBIT 55NS 28CDIP |

| IDT71256S55P | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT71256S55TDB | 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 256KBIT 55NS 28CDIP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。