- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄353744 > IDT7005S55J (INTEGRATED DEVICE TECHNOLOGY INC) Synchronous DC-DC MOSFET Driver; ; No of Pins: 8; Container: Tape & Reel PDF資料下載

參數(shù)資料

| 型號(hào): | IDT7005S55J |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | Synchronous DC-DC MOSFET Driver; ; No of Pins: 8; Container: Tape & Reel |

| 中文描述: | 8K X 8 DUAL-PORT SRAM, 55 ns, PQCC68 |

| 封裝: | 0.950 X 0.950 INCH, 0.120 INCH HEIGHT, PLASTIC, LCC-68 |

| 文件頁(yè)數(shù): | 20/20頁(yè) |

| 文件大?。?/td> | 265K |

| 代理商: | IDT7005S55J |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)

IDT7005S/L

HIGH-SPEED 8K x 8 DUAL-PORT STATIC RAM

MILITARY AND COMMERCIAL TEMPERATURE RANGES

6.06

9

IDT7005X15

IDT7005X17

IDT7005X20

IDT7005X25

Com'l. Only

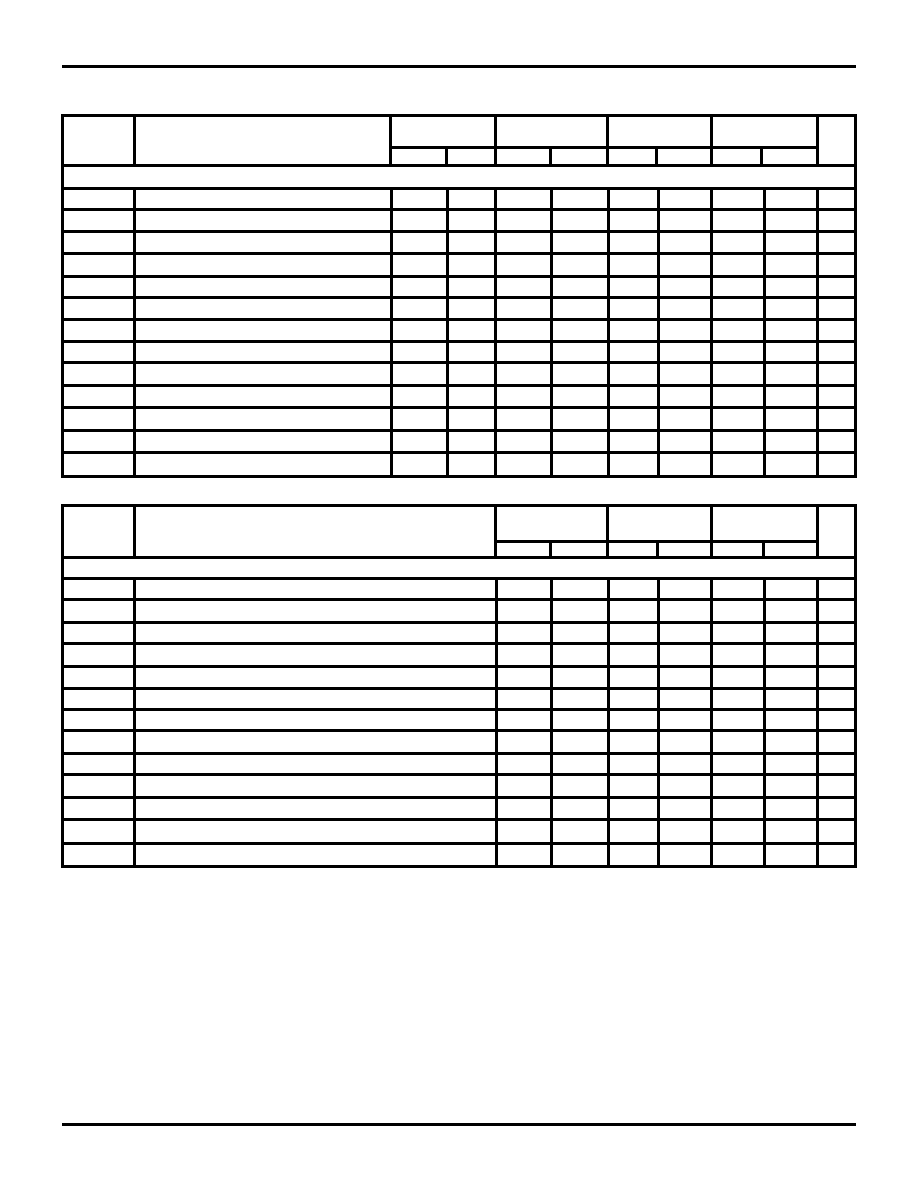

Symbol

Parameter

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Unit

WRITE CYCLE

tWC

Write Cycle Time

15

—

17

—

20

—

25

—

ns

tEW

Chip Enable to End-of-Write

(3)

12

—

12

—

15

—

20

—

ns

tAW

Address Valid to End-of-Write

12

—

12

—

15

—

20

—

ns

tAS

Address Set-up Time

(3)

0

—

0

—

0

—

0

—

ns

tWP

Write Pulse Width

12

—

12

—

15

—

20

—

ns

tWR

Write Recovery Time

0

—

0

—

0

—

0

—

ns

tDW

Data Valid to End-of-Write

10

—

10

—

15

—

15

—

ns

tHZ

Output High-Z Time

(1, 2)

—

10

—

10

—

12

—

15

ns

tDH

Data Hold Time

(4)

0

—

0

—

0

—

0

—

ns

tWZ

Write Enable to Output in High-Z

(1, 2)

—

10

—

10

—

12

—

15

ns

tOW

Output Active from End-of-Write

(1, 2, 4)

0

—

0

—

0

—

0

—

ns

tSWRD

SEM Flag Write to Read Time

5

—

5

—

5

—

5

—

ns

tSPS

SEM Flag Contention Window

5

—

5

—

5

—

5

—

ns

IDT7005X35

IDT7005X55

IDT7005X70

Mil. Only

Symbol

Parameter

Min.

Max.

Min.

Max.

Min.

Max.

Unit

WRITE CYCLE

tWC

Write Cycle Time

35

—

55

—

70

—

ns

tEW

Chip Enable to End-of-Write

(3)

30

—

45

—

50

—

ns

tAW

Address Valid to End-of-Write

30

—

45

—

50

—

ns

tAS

Address Set-up Time

(3)

0—

ns

tWP

Write Pulse Width

25

—

40

—

50

—

ns

tWR

Write Recovery Time

0

—

0

—

0

—

ns

tDW

Data Valid to End-of-Write

15

—

30

—

40

—

ns

tHZ

Output High-Z Time

(1, 2)

—15—25

—30

ns

tDH

Data Hold Time

(4)

0—

ns

tWZ

Write Enable to Output in High-Z

(1, 2)

—15—25

—30

ns

tOW

Output Active from End-of-Write

(1, 2, 4)

0—

ns

tSWRD

SEM Flag Write to Read Time

5

—

5

—

5

—

ns

tSPS

SEM Flag Contention Window

5

—

5

—

5

—

ns

NOTES:

2738 tbl 14

1. Transition is measured

±500mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

2. This parameter is guaranteed by device characterization but is not production tested.

3. To access RAM,

CE = VIL, SEM = VIH. To access semaphore, CE = VIH and SEM = VIL. Either condition must be valid for the entire tEW time.

4. The specification for tDH must be met by the device supplying write data to the RAM under all operating conditions. Although tDH and tOW values will vary

over voltage and temperature, the actual tDH will always be smaller than the actual tOW.

5. "X" in part numbers indicates power rating (S or L).

AC ELECTRICAL CHARACTERISTICS OVER THE

OPERATING TEMPERATURE AND SUPPLY VOLTAGE (5)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT70V05S25J | HIGH-SPEED 3.3V 8K x 8 DUAL-PORT STATIC RAM |

| IDT70V05S25PF | HIGH-SPEED 3.3V 8K x 8 DUAL-PORT STATIC RAM |

| IDT70V05S35G | HIGH-SPEED 3.3V 8K x 8 DUAL-PORT STATIC RAM |

| IDT70V05S35J | HIGH-SPEED 3.3V 8K x 8 DUAL-PORT STATIC RAM |

| IDT70V05S35PF | HIGH-SPEED 3.3V 8K x 8 DUAL-PORT STATIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT7005S55J8 | 功能描述:IC SRAM 64KBIT 55NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:72 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SRAM - 同步 存儲(chǔ)容量:9M(256K x 36) 速度:75ns 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 封裝/外殼:100-LQFP 供應(yīng)商設(shè)備封裝:100-TQFP(14x14) 包裝:托盤 其它名稱:71V67703S75PFGI |

| IDT7005S55JB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:HIGH-SPEED 8K x 8 DUAL-PORT STATIC RAM |

| IDT7005S55JI | 功能描述:IC SRAM 64KBIT 55NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:45 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SRAM - 雙端口,異步 存儲(chǔ)容量:128K(8K x 16) 速度:15ns 接口:并聯(lián) 電源電壓:3 V ~ 3.6 V 工作溫度:0°C ~ 70°C 封裝/外殼:100-LQFP 供應(yīng)商設(shè)備封裝:100-TQFP(14x14) 包裝:托盤 其它名稱:70V25S15PF |

| IDT7005S55JI8 | 功能描述:IC SRAM 64KBIT 55NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:72 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SRAM - 同步 存儲(chǔ)容量:9M(256K x 36) 速度:75ns 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 封裝/外殼:100-LQFP 供應(yīng)商設(shè)備封裝:100-TQFP(14x14) 包裝:托盤 其它名稱:71V67703S75PFGI |

| IDT7005S55L68 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。