- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67710 > ICSSSTUF32864YHLFT (INTEGRATED DEVICE TECHNOLOGY INC) SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 PDF資料下載

參數(shù)資料

| 型號(hào): | ICSSSTUF32864YHLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 鎖存器 |

| 英文描述: | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| 封裝: | MO-205CC, BGA-96 |

| 文件頁數(shù): | 10/11頁 |

| 文件大小: | 110K |

| 代理商: | ICSSSTUF32864YHLFT |

8

ICSSSTUF32864

0880A—04/16/04

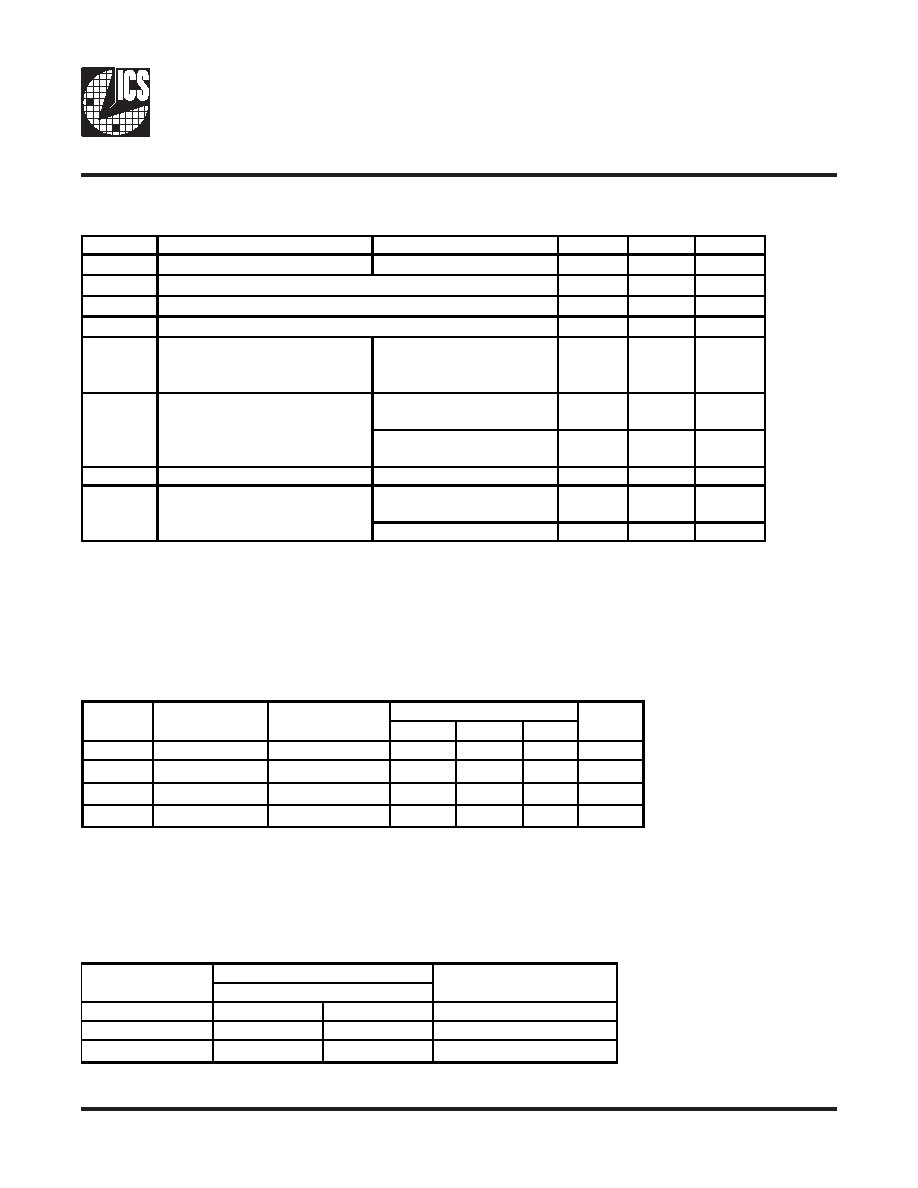

Switching Characteristics

(over recommended operating free-air temperature range, unless otherwise noted)

MIN

TYP

MAX

fmax

270

MHz

tPDM

1

CLK, CLK#

Q

1.41

2.0

ns

tPDMSS

2

CLK, CLK#

Q

tphl

RESET#

Q

3

ns

Notes: 1. Includes 350ps test-load transmission-line delay

2. Guaranteed by design, not 100% tested in production.

SYMBOL

VDD = 1.8V ±0.1V

UNITS

From

(Input)

To

(Output)

Output Buffer Characteristics

Output edge rates over recommended operating free-air temperature range (See figure 7)

MIN

MAX

dV/dt_r

1

4

V/ns

dV/dt_f

1

4

V/ns

dV/dt_

1

1V/ns

1. Difference between dV/dt_r (rising edge rate) and dV/dt_f (falling edge rate)

PARAMETER

VDD = 1.8V ± 0.1V

UNIT

Timing Requirements

(over recommended operating free-air temperature range, unless otherwise noted)

SYMBOL

PARAMETERS

MIN

MAX

UNITS

fclock

Clock frequency

270

MHz

tW

1ns

tACT

TBD

ns

tINACT

TBD

ns

Setup time

DCS before CK, CK

↓, CSR

high; CSR before CK, CK

↓,

DCS high

0.7

ns

DCS before CK, CK

↓, CSR

Low

0.5

ns

DODT, DCKE and data

before CK, CK

↓

0.5

ns

Setup time

PAR_IN before CK, CK

↓

ns

DCS, DODT, DCKE and

data after CK, CK

↓

0.50

ns

PAR_IN after CK, CK

↓

0.50

ns

1 - Guaranteed by design, not 100% tested in production.

2 - For data signal input slew rate of 1V/ns.

4 - CLK/CLK# signal input slew rate of 1V/ns.

Pulse duration, CK, CK High or Low

Differential inputs active time (See notes 1 and 2)

Differential inputs inactive time (See notes 1 and 3)

Hold time

tSU

th

Notes:

3 - For data signal input slew rate of 0.5V/ns and < 1V/ns.

Setup time

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICSSSTUF32866EHT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32866EHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTVA16859CK-LF | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, QCC56 |

| ICSSSTVA16859CK | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, QCC56 |

| ICSSSTVA16859CGLF-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICSSSTV16857 | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16857CG-T | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16857YG-T | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16857YL-T | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16859 | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 13-Bit to 26-Bit Registered Buffer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。