- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67707 > ICS94236YFLF-T (INTEGRATED DEVICE TECHNOLOGY INC) 150 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF資料下載

參數(shù)資料

| 型號: | ICS94236YFLF-T |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 150 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封裝: | 0.300 INCH, MO-118, SSOP-48 |

| 文件頁數(shù): | 14/17頁 |

| 文件大小: | 142K |

| 代理商: | ICS94236YFLF-T |

6

ICS94236

0451A—01/10/03

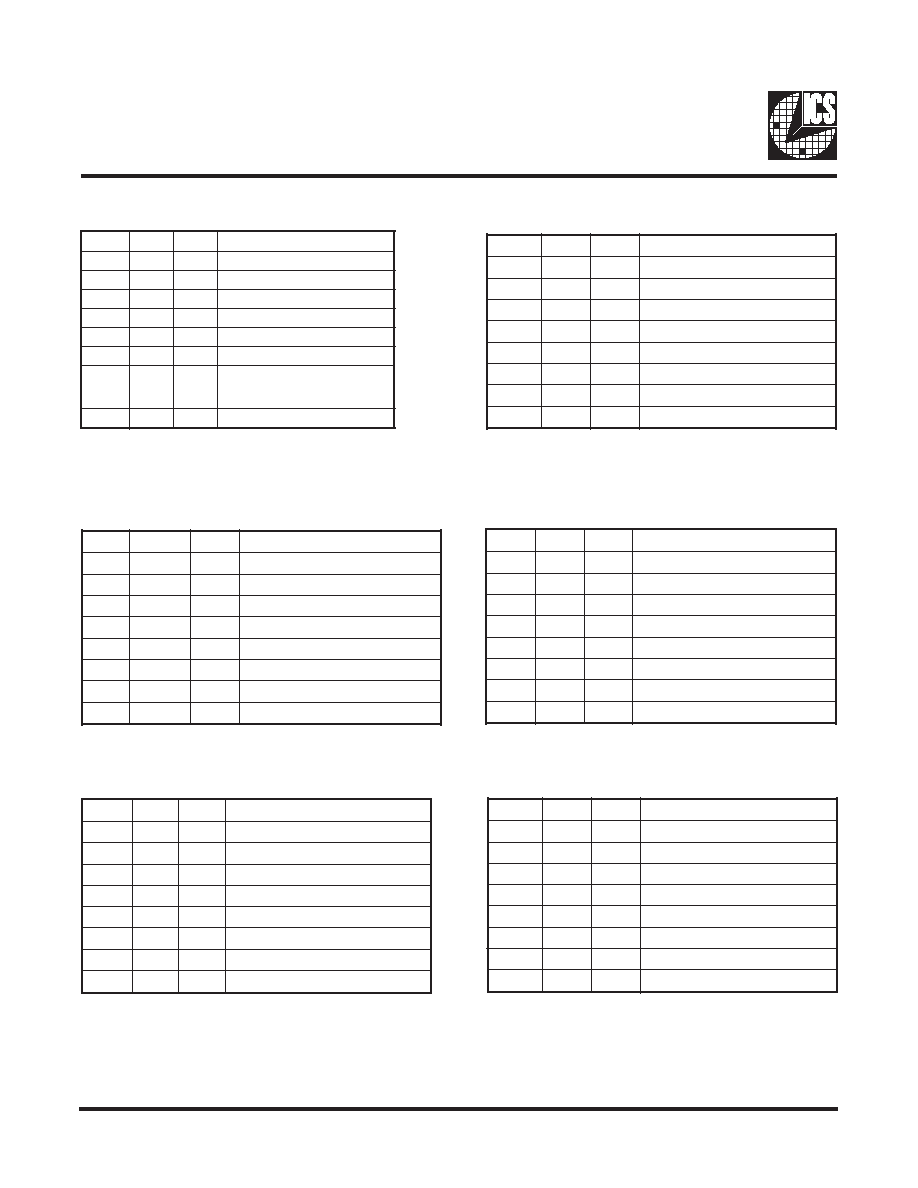

Byte 1: CPU, Active/Inactive Register

(1= enable, 0 = disable)

T

I

B#

N

I

PD

W

PN

O

I

T

P

I

R

C

S

E

D

7

t

i

B-

X

#

2

S

F

6

t

i

B6

41

K

L

C

U

P

C

5

t

i

B-

1

)

d

e

v

r

e

s

e

R

(

4

t

i

B-

X

#

3

S

F

3

t

i

B0

41

T

U

O

_

M

A

R

D

S

2

t

i

B-

X

#

)

#

8

4

_

4

2

L

E

S

(

1

t

i

B4

4

,

3

41

h

t

o

b

(

e

l

b

a

n

e

0

K

L

C

U

P

C

d

n

a

"

e

u

r

T

"

.

r

i

a

p

l

a

i

t

n

e

r

e

f

i

d

)

"

y

r

a

t

n

e

m

i

l

p

m

o

C

0

t

i

B-

1

*

)

d

e

v

r

e

s

e

R

(

Byte 2: PCI, Active/Inactive Register

(1= enable, 0 = disable)

T

I

B#

N

I

PD

W

PN

O

I

T

P

I

R

C

S

E

D

7

t

i

B-

X

#

0

S

F

6

t

i

B7

1

F

_

K

L

C

I

C

P

5

t

i

B-

1

)

d

e

v

r

e

s

e

R

(

4

t

i

B3

11

4

K

L

C

I

C

P

3

t

i

B2

11

3

K

L

C

I

C

P

2

t

i

B1

11

2

K

L

C

I

C

P

1

t

i

B0

11

1

K

L

C

I

C

P

0

t

i

B8

1

0

K

L

C

I

C

P

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

2. Latched Frequency Selects (FS#) will be inverted logic

load of the input frequency select pin conditions.

T

I

B#

N

I

PD

W

PN

O

I

T

P

I

R

C

S

E

D

7

t

i

B8

21

7

M

A

R

D

S

6

t

i

B9

21

6

M

A

R

D

S

5

t

i

B1

31

5

M

A

R

D

S

4

t

i

B2

31

4

M

A

R

D

S

3

t

i

B4

31

3

M

A

R

D

S

2

t

i

B5

31

2

M

A

R

D

S

1

t

i

B7

31

1

M

A

R

D

S

0

t

i

B8

31

0

M

A

R

D

S

Byte 4: SDRAM , Active/Inactive Register

(1= enable, 0 = disable)

T

I

B#

N

I

PD

W

PN

O

I

T

P

I

R

C

S

E

D

7

t

i

B-

1

)

d

e

v

r

e

s

e

R

(

6

t

i

B-

1

)

d

e

v

r

e

s

e

R

(

5

t

i

B-

1

)

d

e

v

r

e

s

e

R

(

4

t

i

B-

X

e

d

o

M

3

t

i

B-

X

#

1

S

F

2

t

i

B-

1

)

d

e

v

r

e

s

e

R

(

1

t

i

B8

41

1

F

E

R

0

t

i

B2

1

0

F

E

R

Byte 5: Peripheral , Active/Inactive Register

(1= enable, 0 = disable)

Byte 3: SDRAM, Active/Inactive Register

(1= enable, 0 = disable)

T

I

B#

N

I

PD

W

PN

O

I

T

P

I

R

C

S

E

D

7

t

i

B-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

6

t

i

B-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

5

t

i

B-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

4

t

i

B-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

3

t

i

B-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

2

t

i

B-

1

)

e

t

o

N

(

d

e

v

r

e

s

e

R

1

t

i

B-

1

)

e

t

o

N

(

d

e

v

r

e

s

e

R

0

t

i

B-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

Byte 6: Peripheral , Active/Inactive Register

(1= enable, 0 = disable)

Note: Don’t write into this register, writing into this

register can cause malfunction

T

I

B#

N

I

PD

W

PN

O

I

T

P

I

R

C

S

E

D

7

t

i

B-

1

)

d

e

v

r

e

s

e

R

(

6

t

i

B-

1

)

d

e

v

r

e

s

e

R

(

5

t

i

B6

21

z

H

M

8

4

t

i

B5

21

z

H

M

8

4

_

4

2

3

t

i

B7

11

1

M

A

R

D

S

2

t

i

B8

11

0

1

M

A

R

D

S

1

t

i

B0

21

9

M

A

R

D

S

0

t

i

B1

21

8

M

A

R

D

S

Note:

* It is recommended to drive this bit to 0.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS94252YFLF-T | 133.33 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS950104YFT | 166 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS950201YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950201YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950201YF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS94236YF-T | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable System Clock Chip for AMD - K7⑩ processor |

| ICS94241 | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable TCH⑩ for Differential PIII⑩ Processor |

| ICS94241FLF-T | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable TCH⑩ for Differential PIII⑩ Processor |

| ICS948AI147L | 制造商:ICS 制造商全稱:ICS 功能描述:LOW SKEW, 1-TO-12 DIFFERENTIAL-TO-LVCMOS/LVTTL FANOUT BUFFER |

| ICS950104 | 制造商:ICS 制造商全稱:ICS 功能描述:Programmable System Clock Chip for PIII Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。