- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360778 > ICS9148-82 Frequency Generator & Integrated Buffers for PENTIUM/ProTM PDF資料下載

參數(shù)資料

| 型號: | ICS9148-82 |

| 英文描述: | Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| 中文描述: | 頻率發(fā)生器 |

| 文件頁數(shù): | 8/16頁 |

| 文件大小: | 691K |

| 代理商: | ICS9148-82 |

8

ICS9148-02

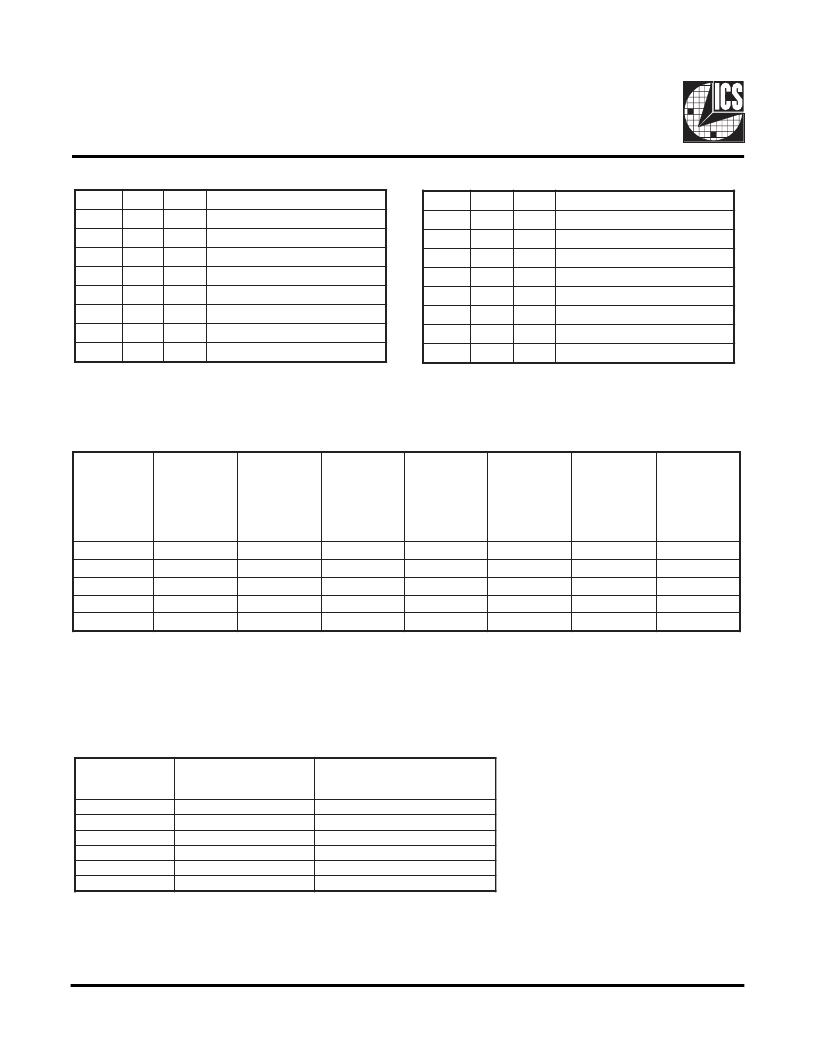

Power Management

Clock Enable Configuration

ICS9148-02 Power Management Requirements

Full clock cycle timing is guaranteed at all times after the system has initially powered up except where noted. During power

up and power down operations using the PWR PD# select pin will not cause clocks of a short or longer pulse than that of the

running clock. The first clock pulse coming out of a stopped clock condition may be slightly distorted due to clock network

charging circuitry. Board routing and signal loading may have a large impact on the initial clock distortion also.

Notes.

1. Clock on latency is defined from when the clock enable goes active to when the first valid clock comes out of the device.

2. Clock off latency is defined from when the clock enable goes inactive to when the last clock is driven low out of the device.

3. Power up latency is when PD# goes inactive (high) to when the first valid clocks are output by the device.

4. Power down has controlled clock counts applicable to CPUCLK, SDRAM, PCICLK only.

The REF and IOAPIC will be stopped independant of these.

L

A

N

G

I

S

E

T

A

T

S

L

A

N

G

I

S

y

c

f

K

L

n

e

L

d

e

C

P

g

n

n

u

e

e

s

g

C

I

1

1

1

1

m

3

m

2

g

n

f

.

N

#

P

O

T

S

_

U

P

C

)

)

)

)

o

p

w

o

D

e

e

a

e

a

D

a

n

E

(

l

m

r

w

o

a

D

n

E

(

(

(

0

1

0

1

r

P

(

2

1

#

P

O

T

S

_

C

P

2

e

O

1

#

N

W

D

_

R

W

P

)

N

0

(

1

3

S

x

a

)

4

Byte 5: Peripheral Clock Register

Notes:

1 = Enabled; 0 = Disabled, outputs held low

Note:

PWD = Power-Up Default

T

I

B

t

B

t

B

t

B

t

B

t

B

t

B

t

B

t

B

#

N

-

-

-

5

4

-

-

1

2

I

P

D

W

1

1

1

1

1

1

1

1

P

N

O

I

T

P

I

R

C

S

E

D

d

d

d

0

d

d

n

A

n

A

7

6

5

4

3

2

1

0

e

e

e

C

e

e

(

(

v

R

v

R

v

R

A

O

I

v

R

v

R

F

E

R

F

E

R

)

a

n

A

(

I

P

)

a

)

a

1

0

#

P

O

T

S

_

U

P

C

#

P

O

T

S

_

C

P

#

N

W

D

_

R

W

P

K

L

C

U

P

C

K

L

C

I

C

P

,

k

,

c

o

C

A

R

,

E

R

P

A

O

M

4

2

4

4

2

4

o

u

R

u

R

u

R

u

R

r

D

S

h

O

M

,

z

z

d

g

g

g

g

C

H

H

e

I

I

A

B

M

p

p

n

n

n

n

n

n

n

n

l

y

C

s

O

C

V

X

0

0

1

1

X

0

1

0

1

0

1

1

1

1

w

w

w

0

0

o

o

o

L

L

L

w

w

0

w

o

0

o

o

L

L

f

n

n

n

n

u

n

n

u

R

n

n

u

R

O

u

f

n

n

n

n

u

n

n

u

R

n

n

u

R

O

u

g

g

g

g

R

R

g

g

g

g

R

R

z

H

M

3

3

z

z

H

H

M

M

6

6

6

6

L

z

H

M

3

3

Byte 6: Optional Register for Future

Notes:

1. Byte 6 is reserved by Integrated Circuit Systems for

future applications.

T

I

B

t

B

t

B

t

B

t

B

t

B

t

B

t

B

t

B

#

N

-

-

-

-

-

-

-

-

I

P

D

W

1

1

1

1

1

1

1

1

P

N

O

I

T

P

I

R

C

S

E

D

d

d

d

d

d

d

d

d

7

6

5

4

3

2

1

0

e

e

e

e

e

e

e

e

v

R

v

R

v

R

v

R

v

R

v

R

v

R

v

R

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS9148-93 | High-Performance Impact<TM> PAL<R> Circuits 28-PLCC 0 to 75 |

| ICS9148yF-82 | High-Performance Impact<TM> PAL<R> Circuits 24-PDIP 0 to 75 |

| ICS9148F-02 | Pentium/ProTM System Clock Chip |

| ICS9148F-03 | Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9148F-11 | Frequency Generator & Integrated Buffers for PENTIUMTM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS9148-93 | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9148B-04 | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9148BF-04 | 制造商:ICS 功能描述:CPU SYSTEM CLOCK GENERATOR, 48 Pin, Plastic, SSOP |

| ICS9148B-F14 | 制造商:ICS 功能描述: 制造商:ICS 功能描述:Electronic Component |

| ICS9148BF-26 | 制造商:ICS 功能描述: 制造商:ICS 功能描述:ELECTRONIC COMPONENT 制造商:Integrated Device Technology Inc 功能描述:CPU SYSTEM CLOCK GENERATOR, 48 Pin, Plastic, SSOP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。