- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360768 > ICS843002CY-31LFT 700MHZ FEMTOCLOCKS⑩ VCXO BASED FREQUENCY TRANSLATOR AND JITTER ATTENUATOR PDF資料下載

參數(shù)資料

| 型號: | ICS843002CY-31LFT |

| 英文描述: | 700MHZ FEMTOCLOCKS⑩ VCXO BASED FREQUENCY TRANSLATOR AND JITTER ATTENUATOR |

| 中文描述: | ⑩VCXO的700MHz的FEMTOCLOCKS基于頻率轉(zhuǎn)換和抖動衰減器 |

| 文件頁數(shù): | 20/27頁 |

| 文件大?。?/td> | 274K |

| 代理商: | ICS843002CY-31LFT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

843002CY-31

www.icst.com/products/hiperclocks.html

REV. B NOVEMBER 22, 2005

20

Integrated

Circuit

Systems, Inc.

ICS843002-31

700MH

Z

F

EMTO

C

LOCKS

VCXO B

ASED

F

REQUENCY

T

RANSLATOR

AND

J

ITTER

A

TTENUATOR

PRELIMINARY

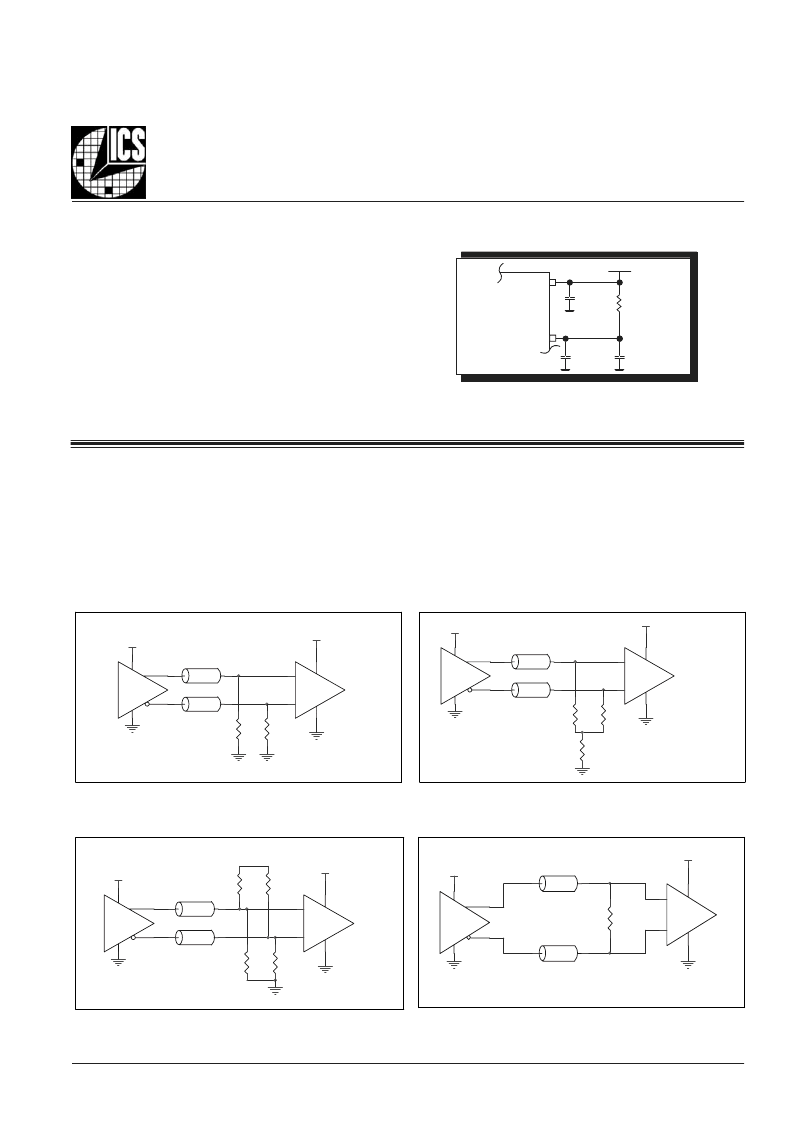

As in any high speed analog circuitry, the power supply pins

are vulnerable to random noise. The ICS843002-31 provides

separate power supplies to isolate any high switching

noise from the outputs to the internal PLL. V

, V

, V

,

and V

should be individually connected to the power sup-

ply plane through vias, and bypass capacitors should be

used for each pin. To achieve optimum jitter performance,

power supply isolation is required.

Figure 3

illustrates how

a 10

Ω

resistor along with a 10

μ

F and a .01

μ

F bypass

capacitor should be connected to each V

CCA

pin.

P

OWER

S

UPPLY

F

ILTERING

T

ECHNIQUES

F

IGURE

3. P

OWER

S

UPPLY

F

ILTERING

10

Ω

V

CCA

10

μ

F

.01

μ

F

3.3V

.01

μ

F

V

CC

F

IGURE

4C.

H

I

P

ER

C

LOCK

S CLK/nCLK I

NPUT

D

RIVEN

BY

3.3V LVPECL D

RIVER

F

IGURE

4B.

H

I

P

ER

C

LOCK

S CLK/nCLK I

NPUT

D

RIVEN

BY

3.3V LVPECL D

RIVER

F

IGURE

4D. H

I

P

ER

C

LOCK

S CLK/nCLK I

NPUT

D

RIVEN

BY

3.3V LVDS D

RIVER

3.3V

R1

50

R3

50

Zo = 50 Ohm

LVPECL

Zo = 50 Ohm

HiPerClockS

CLK

nCLK

3.3V

R2

50

Zo = 50 Ohm

Input

HiPerClockS

CLK

nCLK

3.3V

R3

R2

84

Zo = 50 Ohm

3.3V

R4

LVPECL

R1

84

3.3V

D

IFFERENTIAL

C

LOCK

I

NPUT

I

NTERFACE

The CLK0 /nCLK0 accepts LVDS, LVPECL, LVHSTL, SSTL,

HCSL and other differential signals. Both V

SWING

and V

OH

must

meet the V

and V

input requirements.

show interface examples for the HiPerClockS CLK0/nCLK0

input driven by the most common driver types. The input inter-

faces suggested here are examples only. Please consult with

F

IGURE

4A.

H

I

P

ER

C

LOCK

S CLK/nCLK I

NPUT

D

RIVEN

BY

ICS H

I

P

ER

C

LOCK

S LVHSTL D

RIVER

the vendor of the driver component to confirm the driver termi-

nation requirements. For example in

Figure 4A,

the input ter-

mination applies for ICS HiPerClockS LVHSTL drivers. If you

are using an LVHSTL driver from another vendor, use their

termination recommendation.

1.8V

R2

50

Input

ICS

LVHSTL Driver

R1

50

LVHSTL

3.3V

Zo = 50 Ohm

Zo = 50 Ohm

HiPerClockS

CLK

nCLK

Zo = 50 Ohm

R1

100

3.3V

LVDS_Driver

Zo = 50 Ohm

Receiver

CLK

nCLK

3.3V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS843002CY-31T | 700MHZ FEMTOCLOCKS⑩ VCXO BASED FREQUENCY TRANSLATOR AND JITTER ATTENUATOR |

| ICS843002AGI-01 | FEMTOCLOCKS-TM CRYSTAL-TO- 3.3V, 2.5V LVPECL FREQUENCY SYNTHESIZER |

| ICS843002AGI-01LF | FEMTOCLOCKS-TM CRYSTAL-TO- 3.3V, 2.5V LVPECL FREQUENCY SYNTHESIZER |

| ICS843002AGI-01LFT | FEMTOCLOCKS-TM CRYSTAL-TO- 3.3V, 2.5V LVPECL FREQUENCY SYNTHESIZER |

| ICS843002AGI-01T | FEMTOCLOCKS-TM CRYSTAL-TO- 3.3V, 2.5V LVPECL FREQUENCY SYNTHESIZER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS843002CY-31T | 制造商:ICS 制造商全稱:ICS 功能描述:700MHZ FEMTOCLOCKS⑩ VCXO BASED FREQUENCY TRANSLATOR AND JITTER ATTENUATOR |

| ICS843002I | 制造商:ICS 制造商全稱:ICS 功能描述:FEMTOCLOCKS-TM CRYSTAL-TO-3.3V, 2.5V LVPECL FREQUENCY SYNTHESIZER |

| ICS843002I-01 | 制造商:ICS 制造商全稱:ICS 功能描述:FEMTOCLOCKS-TM CRYSTAL-TO- 3.3V, 2.5V LVPECL FREQUENCY SYNTHESIZER |

| ICS843002I-40 | 制造商:ICS 制造商全稱:ICS 功能描述:175MHZ, FEMTOCLOCKS-TM VCXO BASED SONET/SDH JITTER ATTENUATOR |

| ICS843002I-41 | 制造商:ICS 制造商全稱:ICS 功能描述:700MHz, FEMTOCLOCKS-TM VCXO BASED SONET/SDH JITTER ATTENUATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。