- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224000 > HYS72D64020GR-7.5-X (INFINEON TECHNOLOGIES AG) 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 PDF資料下載

參數(shù)資料

| 型號(hào): | HYS72D64020GR-7.5-X |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 元件分類: | DRAM |

| 英文描述: | 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| 封裝: | DIMM-184 |

| 文件頁(yè)數(shù): | 2/23頁(yè) |

| 文件大小: | 277K |

| 代理商: | HYS72D64020GR-7.5-X |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)

HYS 72Dxx0x0GR

Registered DDR-I SDRAM-Modules

INFINEON Technologies

10

2.01

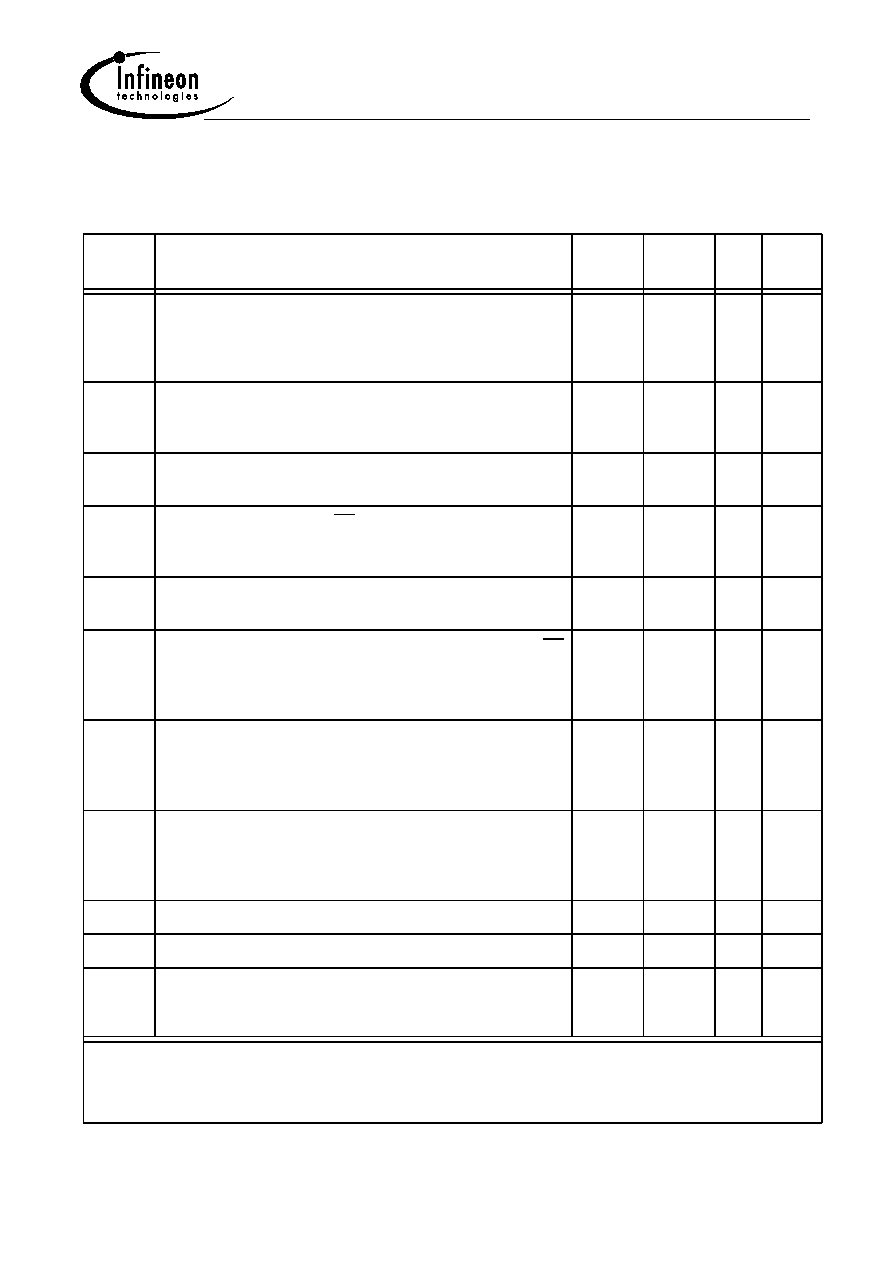

Operating, Standby and Refresh Currents ( for reference only)

(values apply to one SDRAM component )

Symbol

Parameter/Condition

DDR

266A&B

DDR

200

Unit

Notes

I

DD0

Operating Current: one bank; active / precharge; t

RC = tRC

MIN; tCK = tCK MIN; DQ, DM, and DQS inputs changing twice per

clock cycle; address and control inputs changing once per

clock cycle

100

90

mA

1, 2

I

DD1

Operating Current: one bank; active / read / precharge;

Burst = 2; t

RC = tRC MIN; CL = 2.5; tCK = tCK MIN; IOUT = 0mA;

address and control inputs changing once per clock cycle

120

100

mA

1, 2

I

DD2P

Precharge Power-Down Standby Current: all banks

idle; power-down mode; CKE

≤ V

IL MAX; tCK = tCK MIN

20

15

mA

1, 2

I

DD2N

Idle Standby Current: CS

≥ V

IH MIN; all banks idle; CKE ≥

V

IH MIN; tCK = tCK MIN; address and control inputs changing once

per clock cycle

40

35

mA

1, 2

I

DD3P

Active Power-Down Standby Current: one bank active;

power-down mode; CKE

≤ V

IL MAX; tCK = tCK MIN

20

15

mA

1, 2

I

DD3N

Active Standby Current: one bank; active / precharge;CS

≥ V

IH MIN; CKE ≥ VIH MIN; tRC = tRAS MAX; tCK = tCK MIN; DQ, DM,

and DQS inputs changing twice per clock cycle; address and

control inputs changing once per clock cycle

70

60

mA

1, 2

I

DD4R

Operating Current: one bank; Burst = 2; reads; continuous

burst; address and control inputs changing once per clock

cycle; DQ and DQS outputs changing twice per clock cycle; CL

= 2.5; t

CK = tCK MIN; IOUT = 0mA

190

150

mA

1, 2

I

DD4W

Operating Current: one bank; Burst = 2; writes; continuous

burst; address and control inputs changing once per clock

cycle; DQ and DQS inputs changing twice per clock cycle; CL =

2.5; t

CK = tCK MIN

170

130

mA

1, 2

I

DD5

Auto-Refresh Current: t

RC = tRFC MIN

190

180

mA

1, 2

I

DD6

Self-Refresh Current: CKE

≤ 0.2V

3

mA

1, 2, 3

I

DD7

Operating Current: four banks; ffour bank interleaving with

BL=4, address and control inputs randomly changing; 50% of

data changing at every transfer; t

RC = tRC MIN; IOUT = 0mA;

325

250

mA

1, 2

1. I

DD specifications are tested after the device is properly initialized.

2. Input slew rate = 1V/ns

.

3. Enables on-chip refresh and address counters.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72T128000EU-2.5-C2 | 128M X 72 DDR DRAM MODULE, 0.4 ns, DMA240 |

| HYS72T64000EP-3.7-B2 | 64M X 72 DDR DRAM MODULE, DMA240 |

| HZ20-1 | 19.25 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-35 |

| HZ6B1L | 5.65 V, 0.4 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-35 |

| HZ9.1CP | 9.65 V, 1 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-41 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72D64020GR-7-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2.5 V 184-pin Registered DDR-I SDRAM Modules |

| HYS72D64020GR-7-B | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2.5 V 184-pin Registered DDR-I SDRAM Modules |

| HYS72D64020GR-8-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2.5 V 184-pin Registered DDR-I SDRAM Modules |

| HYS72D64020GR-8-B | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2.5 V 184-pin Registered DDR-I SDRAM Modules |

| HYS72D64020GU-7-A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:?512MB (64Mx72) PC2100 2-bank? |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。