- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370806 > HYS72D32300GU-5-B (INFINEON TECHNOLOGIES AG) 184-Pin Unbuffered Dual-In-Line Memory Modules PDF資料下載

參數(shù)資料

| 型號: | HYS72D32300GU-5-B |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 184-Pin Unbuffered Dual-In-Line Memory Modules |

| 中文描述: | 184引腳緩沖雙列內(nèi)存模組 |

| 文件頁數(shù): | 14/51頁 |

| 文件大小: | 1356K |

| 代理商: | HYS72D32300GU-5-B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

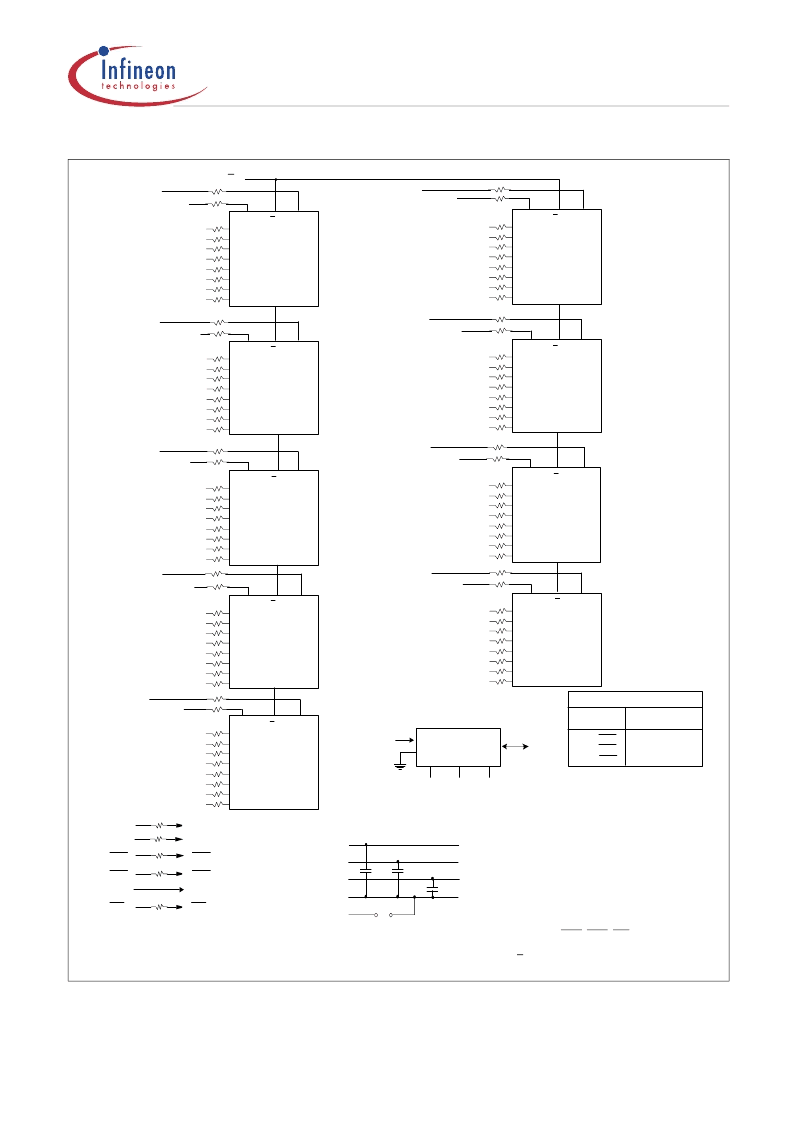

DM7/DQS16

HYS[64/72]D[16x01/32x00/64x20][G/E]U-[5/6/7/8]-B

Unbuffered DDR SDRAM Modules

Pin Configuration

Data Sheet

14

V1.1, 2003-07

DQ4

DQ5

DQ6

DQ7

DQ0

DQ1

DQ2

DQ3

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D0

DM0/DQS9

DQ12

DQ13

DQ14

DQ15

DQ8

DQ9

DQ10

DQ11

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D1

DM1/DQS10

DQ20

DQ21

DQ22

DQ23

DQ16

DQ17

DQ18

DQ19

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D2

DM2/DQS11

DQ28

DQ29

DQ30

DQ31

DQ24

DQ25

DQ26

DQ27

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D3

DM3/DQS12

DQ36

DQ37

DQ38

DQ39

DQ32

DQ33

DQ34

DQ35

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D4

DM4/DQS13

DQ44

DQ45

DQ46

DQ47

DQ40

DQ41

DQ42

DQ43

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D5

DM5/DQS14

DQ52

DQ53

DQ54

DQ55

DQ48

DQ49

DQ50

DQ51

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D6

DQ60

DQ61

DQ62

DQ63

DQ56

DQ57

DQ58

DQ59

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D7

A0 - A13

A0-A13: SDRAMs D0 - D8

A0

Serial PD

A1

A2

SA0

SA1

SA2

SDA

RAS

RAS: SDRAMs D0 - D8

CAS

CAS: SDRAMs D0 - D8

CKE0

CKE: SDRAMs D0 - D8

WE

WE: SDRAMs D0 - D8

S0

S

S

S

S

S

S

S

S

BA0 - BA1

BA0-BA1: SDRAMs D0 - D8

DQS0

DQS

DQS4

DQS1

DQS5

DQS

DQS2

DQS

DQS3

DQS

DM6/DQS15

DQS6

DQS7

CB4

CB5

CB6

CB7

CB0

CB1

CB2

CB3

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D8

S

DQS8

DM8/DQS17

DQS

DQS

DQS

DQS

DQS

* Clock Wiring

Clock

Input

*CK0/CK0

*CK1/CK1

*CK2/CK2

SDRAMs

3 SDRAMs

3 SDRAMs

3 SDRAMs

* Wire per Clock Loading

Table/Wiring Diagrams

V

SS

D0 - D8

V

DD

/V

DDQ

D0 - D8

D0 - D8

V

REF

V

DDID

Strap: see Note 4

Notes:

1. DQ-to-I/O wiring is shown as recommended

but may be changed.

2. DQ/DQS/DM/CKE/S relationships must be

maintained as shown.

3. DQ, DQS, DM/DQS resistors: 22 ohms ± 5%.

4. V

strap connections

(for memory device V

, V

DDQ

):

STRAP OUT (OPEN): V

DDQ

STRAP IN (V

SS

): V

DD

≠

V

DDQ

.

5. BAx, Ax, RAS, CAS, WE resistors: 5.1 ohm

+5%

SCL

WP

SPD

V

DD

SPD

Figure 4

Block Diagram - One Rank 32M

×

72 DDR-I SDRAM DIMM HYS72D32x00GU using

×

8

organized SDRAMs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS64D64320GU-5-B | 184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS72D64320GU-5-B | 184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS72D64320GU-5-C | 184-Pin Unbuffered Double Data Rate SDRAM |

| HYS64D16301GU | 184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS64D16301GU-7-B | 184-Pin Unbuffered Dual-In-Line Memory Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72D32300GU-5-C | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:184-Pin Unbuffered Double Data Rate SDRAM |

| HYS72D32300GU-6-B | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS72D32300GU-6-C | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:184-Pin Unbuffered Double Data Rate SDRAM |

| HYS72D32300HBR-5-C | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:184-Pin Registered Double Data Rate SDRAM Module |

| HYS72D32300HBR-6-C | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:184-Pin Registered Double Data Rate SDRAM Module |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。