- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385426 > HY5DU283222F-33 (HYNIX SEMICONDUCTOR INC) 128M(4Mx32) GDDR SDRAM PDF資料下載

參數(shù)資料

| 型號: | HY5DU283222F-33 |

| 廠商: | HYNIX SEMICONDUCTOR INC |

| 元件分類: | DRAM |

| 英文描述: | 128M(4Mx32) GDDR SDRAM |

| 中文描述: | 4M X 32 DDR DRAM, 0.9 ns, PBGA144 |

| 封裝: | 12 X 12 MM, 0.80 MM PITCH, FBGA-144 |

| 文件頁數(shù): | 24/30頁 |

| 文件大?。?/td> | 359K |

| 代理商: | HY5DU283222F-33 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁

Rev. 1.2/Sep. 02

24

HY5DU283222F

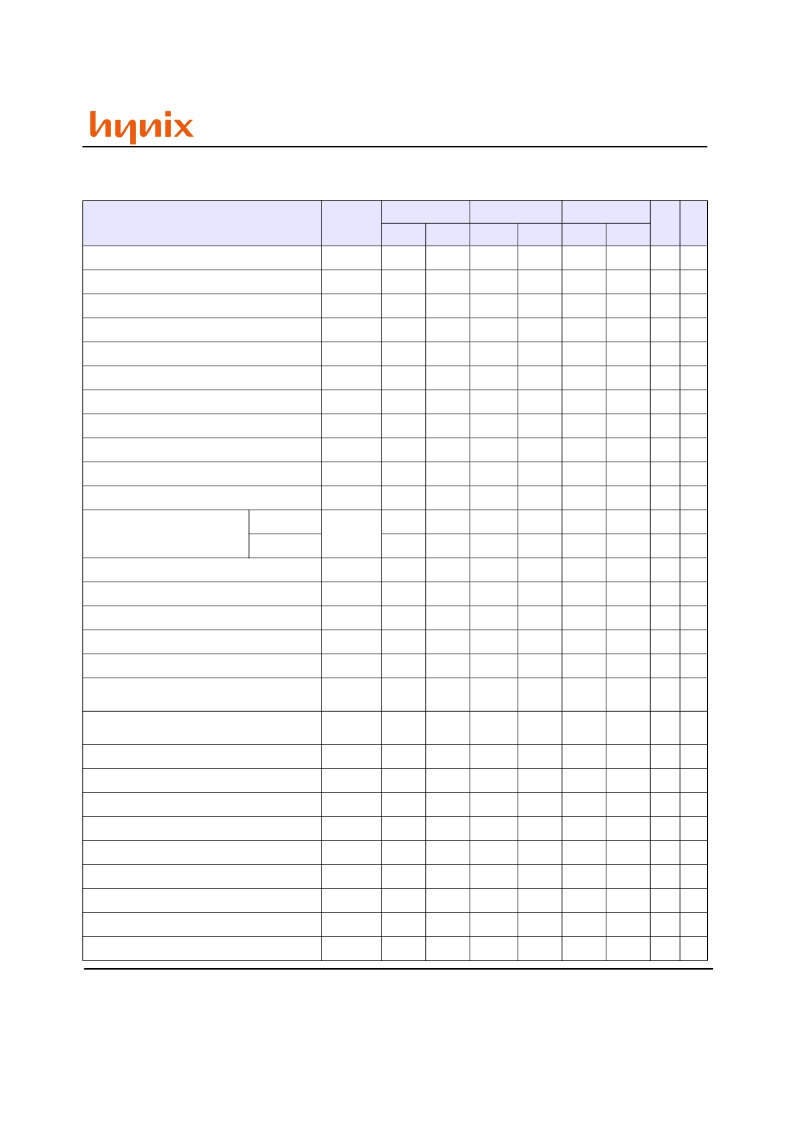

AC CHARACTERISTICS - I

(AC operating conditions unless otherwise noted)

Parameter

Symbol

26

28

33

Unit

Note

Min

Max

Min

Max

Min

Max

Row Cycle Time

t

RC

59.8

-

61.6

-

62.7

-

ns

Auto Refresh Row Cycle Time

t

RFC

65

-

64.4

-

66

-

ns

Row Active Time

t

RAS

41.6

120K

42

120K

42.9

120K

ns

Row Address to Column Address Delay for Read

t

RCDRD

7

-

7

-

6

-

CK

Row Address to Column Address Delay for Write

t

RCDWR

4

-

4

-

3

-

CK

Row Active to Row Active Delay

t

RRD

2

-

2

-

2

-

CK

Column Address to Column Address Delay

t

CCD

1

-

1

-

1

-

CK

Row Precharge Time

t

RP

7

-

7

-

6

-

CK

Write Recovery Time

t

WR

3

-

3

-

3

-

CK

Last Data-In to Read Command

t

DRL

2

-

2

-

2

-

CK

Auto Precharge Write Recovery + Precharge Time

t

DAL

10

-

10

-

9

-

CK

System Clock Cycle Time

CL=4

t

CK

2.6

6

2.8

6

3.3

6

ns

CL=3

-

-

-

-

-

-

ns

Clock High Level Width

t

CH

0.45

0.55

0.45

0.55

0.45

0.55

CK

Clock Low Level Width

t

CL

0.45

0.55

0.45

0.55

0.45

0.55

CK

Data-Out edge to Clock edge Skew

t

AC

-0.9

0.9

-0.9

0.9

-0.9

0.9

ns

DQS-Out edge to Clock edge Skew

t

DQSCK

-0.7

0.7

-0.7

0.7

-0.7

0.7

ns

DQS-Out edge to Data-Out edge Skew

t

DQSQ

-

0.4

-

0.4

-

0.4

ns

Data-Out hold time from DQS

t

QH

tHPmin

-tQHS

-

tHPmin

-tQHS

-

tHPmin

-tQHS

-

ns

1,6

Clock Half Period

t

HP

tCH/L

min

-

tCH/L

min

-

tCH/L

min

-

ns

1,5

Data Hold Skew Factor

t

QHS

-

0.5

-

0.5

-

0.5

ns

6

Input Setup Time

t

IS

0.75

-

0.75

-

0.75

-

ns

2

Input Hold Time

t

IH

0.75

-

0.75

-

0.75

-

ns

2

Write DQS High Level Width

t

DQSH

0.4

0.6

0.4

0.6

0.4

0.6

CK

Write DQS Low Level Width

t

DQSL

0.4

0.6

0.4

0.6

0.4

0.6

CK

Clock to First Rising edge of DQS-In

t

DQSS

0.75

1.25

0.75

1.25

0.75

1.25

CK

Data-In Setup Time to DQS-In (DQ & DM)

t

DS

0.4

-

0.4

-

0.4

-

ns

3

Data-In Hold Time to DQS-In (DQ & DM)

t

DH

0.4

-

0.4

-

0.4

-

ns

3

Read DQS Preamble Time

t

RPRE

0.7

1.1

0.7

1.1

0.7

1.1

CK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY5DU283222F-36 | 128M(4Mx32) GDDR SDRAM |

| HY5DU283222F-4 | 128M(4Mx32) GDDR SDRAM |

| HY5DU283222F-5 | 128M(4Mx32) GDDR SDRAM |

| HY5DU28422BLT-X | 128M-S DDR SDRAM |

| HY5DU28422BT-X | 128M-S DDR SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY5DU283222F-36 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:128M(4Mx32) GDDR SDRAM |

| HY5DU283222F-4 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:128M(4Mx32) GDDR SDRAM |

| HY5DU283222F-5 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:128M(4Mx32) GDDR SDRAM |

| HY5DU283222Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4Mx32|2.5V|4K|4/45/5|DDR SDRAM - 128M |

| HY5DU283222Q-4 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SDRAM|DDR|4X1MX32|CMOS|QFP|100PIN|PLASTIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。