- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385426 > HY5DU281622ET-5 (HYNIX SEMICONDUCTOR INC) 128M(8Mx16) GDDR SDRAM PDF資料下載

參數(shù)資料

| 型號(hào): | HY5DU281622ET-5 |

| 廠商: | HYNIX SEMICONDUCTOR INC |

| 元件分類(lèi): | DRAM |

| 英文描述: | 128M(8Mx16) GDDR SDRAM |

| 中文描述: | 8M X 16 DDR DRAM, 0.65 ns, PDSO66 |

| 封裝: | 0.400 X 0.875 INCH, 0.65 MM PITCH, TSOP2-66 |

| 文件頁(yè)數(shù): | 29/34頁(yè) |

| 文件大小: | 379K |

| 代理商: | HY5DU281622ET-5 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)

Rev. 0.5 / Jan. 2005

29

HY5DU281622ET

N

ote :

1.

This calculation accounts for tDQSQ(max), the pulse width distortion of on-chip circuit and jitter.

2.

Data sampled at the rising edges of the clock : A0~A11, BA0~BA1, CKE, /CS, /RAS, /CAS, /WE.

3.

Data latched at both rising and falling edges of Data Strobes(UDQS,LDQS) : DQ, LDM,UDM.

4.

Minimum of 200 cycles of stable input clocks after Self Refresh Exit command, where CKE is held high, is required to complete

Self Refresh Exit and lock the internal DLL circuit of DDR SDRAM.

5.

Min (tCL, tCH) refers to the smaller of the actual clock low time and the actual clock high time as provided to the device (i.e. this

value can be greater than the minimum specification limits for tCL and tCH).

6. tHP = minimum half clock period for any given cycle and is defined by clock high or clock low (tCH, tCL).

tQHS consists of tDQSQmax, the pulse width distortion of on-chip clock circuits, data pin to pin skew and

output pattern effects, and p-channel to n-channel variation of the output drivers.

7. DQS, DM and DQ input slew rate is specified to prevent double clocking of data and preserve setup and hold times.

Signal transitions through the DC region must be monotonic.

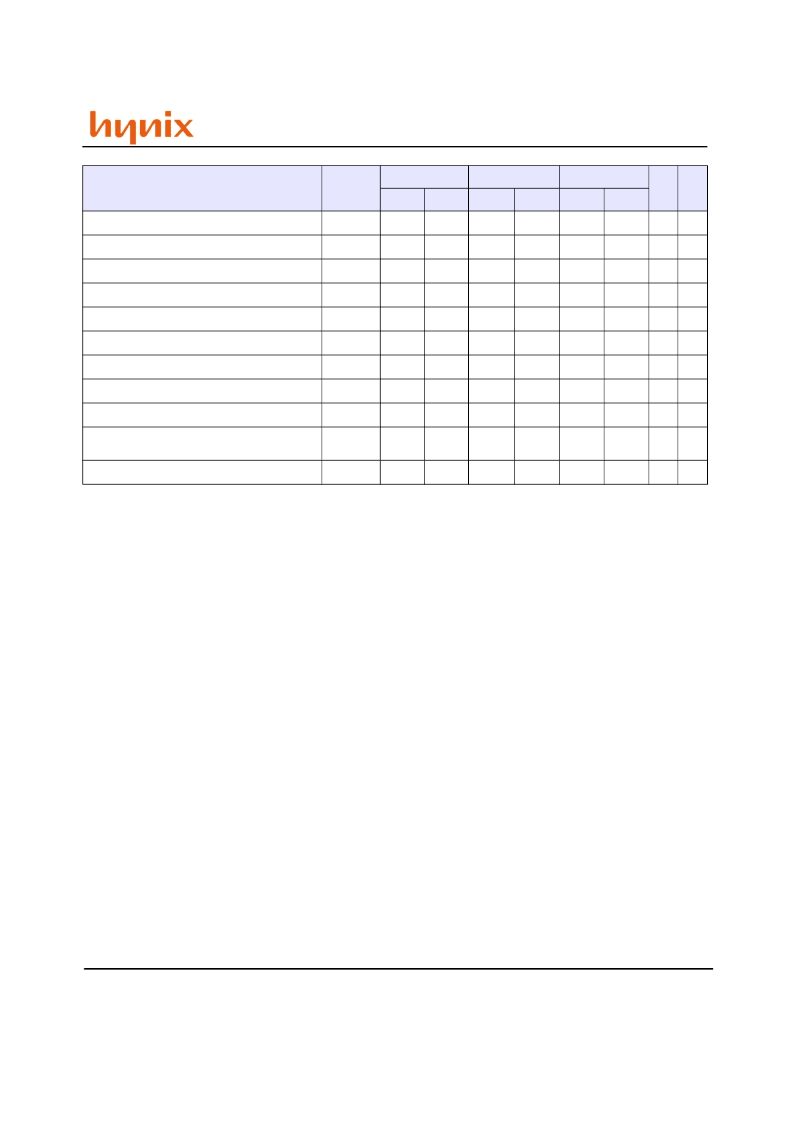

DQS falling edge to CK setup time

tDSS

0.3

-

0.3

-

0.3

-

CK

DQS falling edge hold time from CK

tDSH

0.3

-

0.3

-

0.3

-

CK

Read DQS Preamble Time

t

RPRE

0.9

1.1

0.9

1.1

0.9

1.1

CK

Read DQS Postamble Time

t

RPST

0.4

0.6

0.4

0.6

0.4

0.6

CK

Write DQS Preamble Setup Time

t

WPRES

0

-

0

-

0

-

ns

Write DQS Preamble Hold Time

t

WPREH

0.35

-

0.35

-

0.35

-

CK

Write DQS Postamble Time

t

WPST

0.4

0.6

0.4

0.6

0.4

0.6

CK

Mode Register Set Delay

t

MRD

10

-

10

-

10

-

ns

Exit Self Refresh to Any Execute Command

t

XSC

200

-

200

-

200

-

CK

4

Power Down Exit Time

t

PDEX

2tCK

+ tIS

-

2tCK

+ tIS

-

2tCK

+ tIS

-

CK

Average Periodic Refresh Interval

t

REFI

-

7.8

-

7.8

-

7.8

us

Parameter

Symbol

30

33

36

Unit

Note

Min

Max

Min

Max

Min

Max

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY5DU283222AF | 128M(4Mx32) GDDR SDRAM |

| HY5DU283222AF-2 | 128M(4Mx32) GDDR SDRAM |

| HY5DU283222AF-22 | 128M(4Mx32) GDDR SDRAM |

| HY5DU283222AF-25 | 128M(4Mx32) GDDR SDRAM |

| HY5DU283222AF-28 | 128M(4Mx32) GDDR SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY5DU281622ETP | 制造商:HYNIX 制造商全稱(chēng):Hynix Semiconductor 功能描述:128Mb DDR SDRAM |

| HY5DU281622ETP-25 | 制造商:HYNIX 制造商全稱(chēng):Hynix Semiconductor 功能描述:128M(8Mx16) gDDR SDRAM |

| HY5DU281622ETP-26 | 制造商:HYNIX 制造商全稱(chēng):Hynix Semiconductor 功能描述:128M(8Mx16) gDDR SDRAM |

| HY5DU281622ETP-28 | 制造商:HYNIX 制造商全稱(chēng):Hynix Semiconductor 功能描述:128M(8Mx16) gDDR SDRAM |

| HY5DU281622ETP-30 | 制造商:HYNIX 制造商全稱(chēng):Hynix Semiconductor 功能描述:128M(8Mx16) gDDR SDRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。