- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371898 > HSP50306SC-2596 (INTERSIL CORP) Digital QPSK Demodulator PDF資料下載

參數(shù)資料

| 型號: | HSP50306SC-2596 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Digital QPSK Demodulator |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PDSO16 |

| 封裝: | SOIC-16 |

| 文件頁數(shù): | 4/8頁 |

| 文件大小: | 37K |

| 代理商: | HSP50306SC-2596 |

8-275

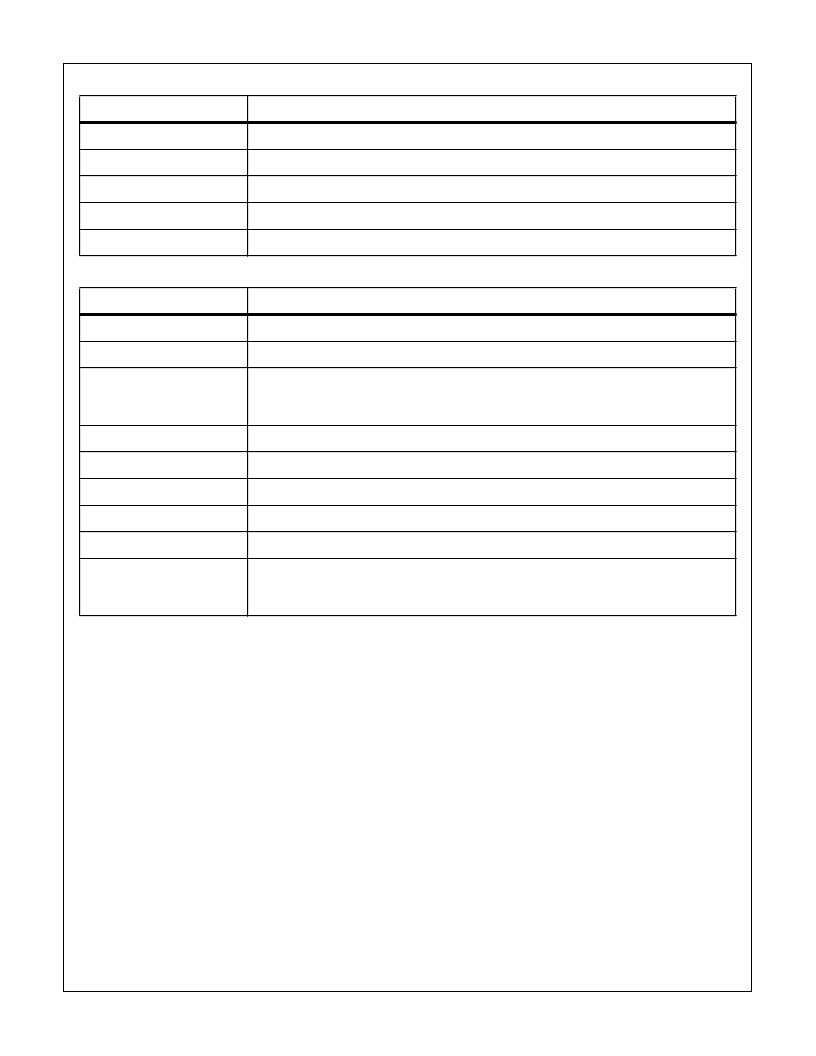

TABLE 1. PERFORMANCE SPECIFICATIONS

SPECIFICATION

PERFORMANCE

BER

Better than 1.0 x 10

-

9

with specified input signal characteristics. See Figure 1.

Acquisition Time

Acquisition within 0.1s from applying an input signal with the specified characteristics.

Carrier Loop Bandwidth

10kHz

Bit Sync Loop Bandwidth

3kHz

Throughput Delay

Less than 6 output bit times.

TABLE 2. INPUT SIGNAL CHARACTERISTICS

(NOTE 1)

PARAMETER

SPECIFICATION

Carrier Frequency

10.7 x 10

6

±

40kHz.

Bit Rate

2.048 x 10

6

±

0.01%.

Modulation Format

QPSK w/differential encoding specified as:

00:

0

o

phase change

01: -90

o

phase change

10: +90

o

phase change

11: 180

o

phase change

(Note 2)

Filtering

Square root of raised cosine matched filtering (

α

= 0.4).

Input RMS Signal Level

Set input p-p signal to full scale on the A/D converter.

Input Data Format

6 bits, offset binary.

Input Clock Frequency

26.97MHz

±

0.015% (Note 3) for -27; 25.6MHz

±

0.015% for -25.

SINAD

>25.5dB SNR (thermal (AWGN)), >28dB (adjacent channel interference).

Multipath Distortion

Total energy in multipath distortion -10dBc

>95% of multipath energy within 2

μ

s from main path. If the multipath changes rapidly, the bit error rate

may exceed the above specification until the equalizer has readjusted.

NOTES:

1. All frequencies are relative to the input clock frequency. For example, the bit rate is actually ~0.075936 * f

CLK

. The frequencies provided

in this document are only valid for a 26.97MHz or 25.6MHz clock.

2. Each pair of input bits is encoded into a phase change relative to the previous symbol. In the HSP50306, the symbol to symbol phase

change is decoded into the transmitted bit pair which is multiplexed into the output data stream.

3. While the device is static CMOS and can be clocked down to close to DC, the specified range indicates the accuracy needed to maintain

the data rate inside the bit sync tracking loop bandwidth assuming 50ppm tx and 100ppm rx crystal accuracies.

HSP50306

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP50306SC-27 | Digital QPSK Demodulator |

| HSP50306SC-2796 | Digital QPSK Demodulator |

| HSP50306 | Digital QPSK Demodulator(數(shù)字QPSK解調(diào)器) |

| HSP9501JC-25 | Programmable Data Buffer |

| HSP9501JC-2596 | Programmable Data Buffer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50306SC-27 | 制造商:Rochester Electronics LLC 功能描述:QPSK DEMODULATOR 16 LEAD SOIC - Bulk |

| HSP50306SC-27 WAF | 制造商:Intersil Corporation 功能描述: |

| HSP50306SC-2796 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HSP50307 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Burst QPSK Modulator |

| HSP50307_00 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Burst QPSK Modulator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。