- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370684 > HS7516 16-Bit Multiplying DACs PDF資料下載

參數(shù)資料

| 型號(hào): | HS7516 |

| 英文描述: | 16-Bit Multiplying DACs |

| 中文描述: | 16位乘法數(shù)模轉(zhuǎn)換器 |

| 文件頁(yè)數(shù): | 6/8頁(yè) |

| 文件大小: | 130K |

| 代理商: | HS7516 |

Corporation

SIGNAL PROCESSING EXCELLENCE

132

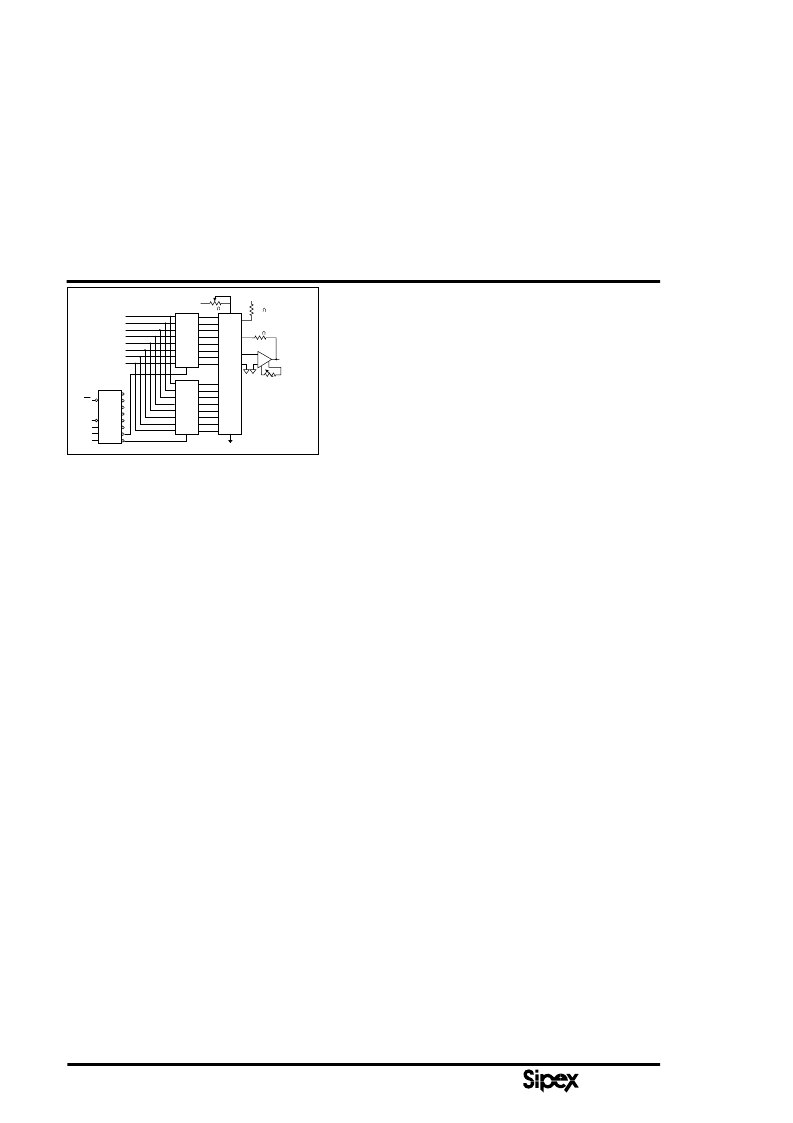

Figure 4. Microprocessor Interface to SP7514

D0

D1

D2

D3

D4

D5

D6

D7

CLK

74273

VREF

(+ 25V MAX)

LSB

15

14

13

12

11

10

9

HS3160

SP7514/

7516

8

7

6

5

4

3

2

D0

D1

D2

D3

D4

D5

D6

D7

74273

CLK

MSBGND

LATCHES

ADDRESS DECODER

G2A

74LS138

G2B

C

B

A

D0

D1

D2

D3

D4

D5

D6

D7

+

–

200

470

3

DD

V

400

WR

BDSEL

A2

A1

A0

VREF

VDD

+

R

I01

I02

UNIPOLAR MODE

(2-QUADRANT)

6

2

3

A1

0 VOUT

(1-2

- N

)

R0S

F

HS3160,

small values for C

must be used. Resis-

tor R

can be added, this will parallel R

decreasing

the effective resistance. If C

is reduced the band-

width will be increased and settling time decreased.

However a system penalty for lowering C

is to

increase noise gain. The tradeoff is noise vs. set-

tling time. If R

is added then a large value (1

μ

F or

greater) non-polarized capacitor C

should be added

in series with R

to eliminate any DC drifts. If

settling time is not important, eliminate R

p

and C

p

,

and adjust C

f

to prevent overshoot.

Output Offset

In most applications, the output of the DAC is fed

into an amplifier to convert the DAC’s current

output to voltage. A little known and not com-

monly discussed parameter is the linearity error

versus offset voltage of the output amplifier. All

CMOS DAC’s must operate into a virtual ground,

i.e., the summing junction of an op amp. Any

amplifier’s offset from the amplifier will appear as

an error at the output (which can be related to

LSB’s of error).

Most all CMOS DAC’s currently available are

implemented using an R-2R ladder network. The

formula for nonlinearity is typically 0.67mV/mV

(not derived here). However the

SP7516

has a

coefficient of only 0.065mV/mV

. This is due to

the decoding technique described earlier. CMOS

DAC applications notes (including this one) al-

ways show a potentiometer used to null out the

amplifier’s offset. If an amplifier is chosen having

‘pretrimmed’ offset it may be possible to eliminate

this component. Consider the following calcula-

tions:

1.

Using LF441A amplifier (low power - 741 pinout)

2.

Specified offset: 0.5mV max

3.

Temperature coefficient of input offset: 10

μ

V/

°

C max

V

OS

max (0

°

C to 70

°

C)

= 0.5mV + (70

μ

V)10

= 1.2mV

Add'l nonlinearity (max)

= 1.2mV x 0.065mV/mV

= 78

μ

V (1/2 LSB @ 16 Bits!)

Where: 78

μ

V = 1/2 LSB @ 16 Bits (10V range)

Via the above configuration, the

SP7516/HS3160

can be used to divide an analog signal by digital

code (i.e. for digitally controlled gain). The trans-

fer function is given in

Table 2,

where the value of

each bit is 0 or 1. Division by all “0”s is undefined

and causes the op amp to saturate.

Following the decoded section of the DAC a

standard binary weighted R-2R approach is used.

This divides each of the 16 levels (or 6.25% of

F.S.) into 4096 discrete levels (the 12 LSB’s).

Output Capacitance

The

SP7516/HS3160

have very low output ca-

pacitance (C

). This is specified both with all

switches ON and all switches OFF. Output capaci-

tance varies from 50pF to 100pF over all input

codes. This low capacitance is due in part to the

decoding technique used. Smaller switches are

used with resulting less capacitance. Three impor-

tant system characteristics are affected by C

and

C

; namely digital feedthrough, settling time,

and bandwidth. The DAC output equivalent cir-

cuit can be represented as shown in

Figure 1

.

Digital feedthrough is the change in analog output

due to the toggling conditions on the converter

input data lines when the analog input V

is at

0V. The

SP7516/HS3160

very low C

and there-

fore will yield low digital feedthrough. Inputs to

the DAC can be buffered. This input latch with

microprocessor control is shown in

Figure 4

.

Settling time is directly affected by C

. In

Figure

1

, C

combines with R

to add a pole to the open

loop response, reducing bandwidth and causing

excessive phase shift - which could result in

ringing and/or oscillation. A feedback capaci-

tor, C

must be added to restore stability. Even with

C

, there is still a zero-pole mismatch due to R

C

O

which is code dependent. This code dependent

mismatch is minimized when C

R

= R

C

. How-

ever C

must now be made larger to compensate for

worst case

R

C

- resulting in reduced bandwidth

and increased settling time. With the

SP7516/

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HS326-SERIES | Peripheral IC |

| HS336-SERIES | Peripheral IC |

| HS3300 | Peripheral IC |

| HS33806 | 12-Bit Digital-to-Analog Converter |

| HS3402 | Small Signal Transistors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HS751KJ | 制造商:Arcol 功能描述:HS75 Al house wirewound resistor,1K 75W |

| HS751RJ | 制造商:Arcol 功能描述:HS75 Al house wirewound resistor,1R 75W |

| HS75220RJ | 制造商:Arcol 功能描述:HS75 Al house wirewoundresistor,220R 75W |

| HS7522RJ | 制造商:Arcol 功能描述:HS75 Al house wirewound resistor,22R 75W |

| HS7528AD | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Digital-to-Analog Converter |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。