- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371882 > HPLL-8001-TR1 Rack/panel connectors, Crimping type; HRS No: 221-0107-1 00; Connector Type: Wire; Contact Gender: Male; Applicable Cable: Conductor AWG#24 to #28; Termination Style: Crimping; Current Rating(Amps)(Max.): 3; Mating/Unmating Cycles: 1000; Contact Mating Area Plating: Gold; General Description: Crimp contact; For Signal PDF資料下載

參數(shù)資料

| 型號: | HPLL-8001-TR1 |

| 英文描述: | Rack/panel connectors, Crimping type; HRS No: 221-0107-1 00; Connector Type: Wire; Contact Gender: Male; Applicable Cable: Conductor AWG#24 to #28; Termination Style: Crimping; Current Rating(Amps)(Max.): 3; Mating/Unmating Cycles: 1000; Contact Mating Area Plating: Gold; General Description: Crimp contact; For Signal |

| 中文描述: | 串行輸入頻率合成器 |

| 文件頁數(shù): | 7/12頁 |

| 文件大?。?/td> | 91K |

| 代理商: | HPLL-8001-TR1 |

7

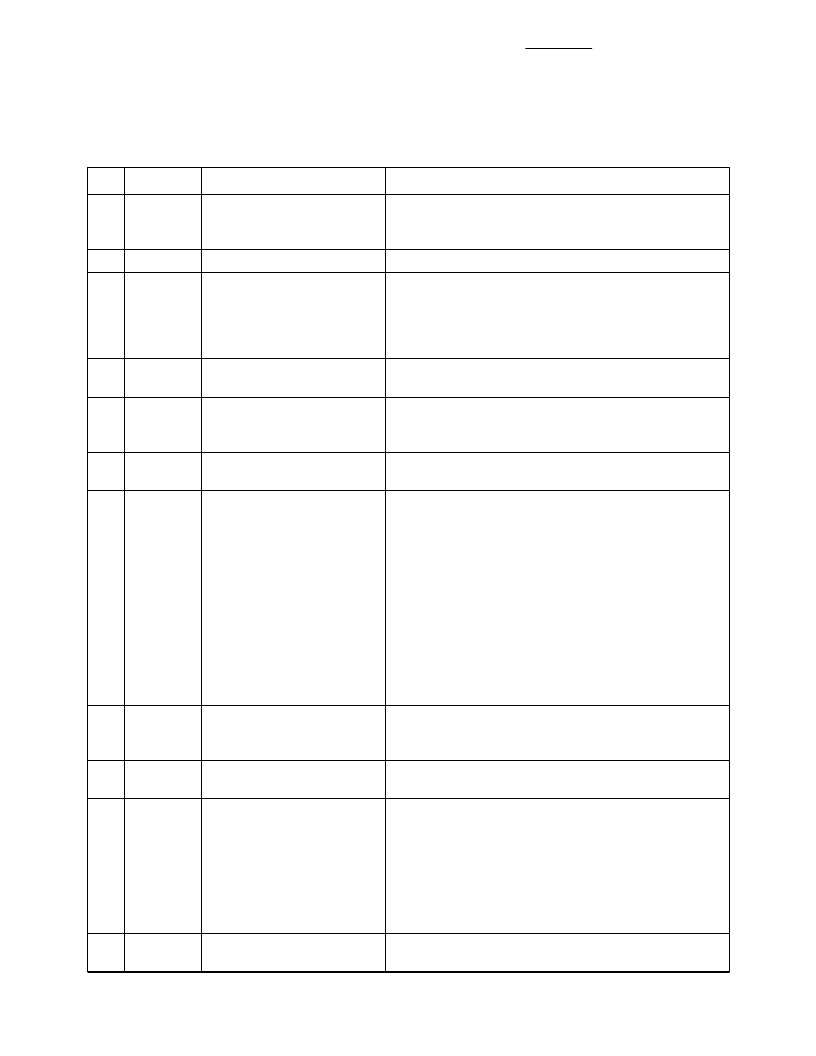

HPLL-8001 Pin Description Table

No.

Mnemonic

Description

Typical Signal

1

REFI

Reference Frequency

High sensitivity preamplifier input for the r-counter.

The input can be AC-coupled for small input signals or

DC-coupled for large input signals.

2

VSS

Ground for digital logic

0 V

3

EN

3-wire interface: Enable

Enable line of the serial interface with internal pull-up

resistor. When EN=H, the input signal CLK and DATA are

internally disabled. When EN=L, the received data is

transferred to the latches on the positive edge of the EN

signal.

4

DATA

3-wire interface: Data

Serial DATA input with internal pull-up resistor. The last two

bits before the EN-signal define the destination address.

5

CLK

3-wire interface: Clock

Clock line with internal pull-up resistor. The serial DATA is

read into the internal shift register on the positive edge (see

pulse diagram for serial data control).

6

VDD

Positive supply voltage for

digital logic

7

MOD

Modulus Control

For an external dual modulus prescaler. The modulus output

is low at the beginning of the cycle. When the a-counter has

reached its set value, MOD switches to high. When the n-

counter has reached its set value, MOD switches to low and

the cycle starts again. When the prescaler has the counter

factor P or P+1 (P for MOD=H, P+1 for MOD=L), the overall

scaling factor is NP+A. The value of the a-counter must be

smaller than that of the n-counter. The trigger edge of the

modulus signal to the input signal can be selected (see

programming tables and MOD A, B) according to the needs

of the prescaler.

In single modulus operation and for standby operation,

the output is low.

8

VCOI

VCO frequency

High sensitivity preamplifier input for the n-counter. The

input can be AC-coupled for small input signals or

DC-coupled for large input signals.

9

AVSS

Ground for analog logic

Pins VDD and AVDD and also pins VSS and AVSS must have

the same power supply voltage.

10

PD

Phase detector

Tristate charge pump output. The level of the charge pump

output current can be programmed using the digital interface.

frequency F

V

<F

R

or F

V

lagging: p source active

frequency F

V

>F

R

or F

V

leading: n source active

frequency F

V

=F

R

& PLL locked: PD tristate

standby mode: PD tristate

The polarity of the output signals of the phase detector can be

programmed.

11

AVDD

Positive supply voltage for

analog logic

相關PDF資料 |

PDF描述 |

|---|---|

| HPM1502 | Analog IC |

| HPM2001 | Analog IC |

| HPMA-0200 | Microwave/Millimeter Wave Amplifier |

| HPMA-0211 | Microwave/Millimeter Wave Amplifier |

| HPMA-0235 | Microwave/Millimeter Wave Amplifier |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HPLM200 | 制造商:Thomas & Betts 功能描述:DEPTH ADJST SUPPRT-HP1612B/HP2015B |

| HP-LP-000-K | 制造商:PacTec 功能描述:Enclosure Kit, Plastic, Plastic, Black, 5.75 in. L x 3.60 in. W x 0.81 in. H |

| HPL-R0001 | 制造商:OTTO Engineering Inc 功能描述:1-4V PROP.ROCKER W/ |

| HPL-R0005 | 制造商:OTTO Engineering Inc 功能描述:HPL-R32224R STD WITH |

| HPL-R0008 | 制造商:OTTO Engineering Inc 功能描述:HPL-R32122R EX WITH |

發(fā)布緊急采購,3分鐘左右您將得到回復。