- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370661 > HPC3130APBMQUADFLAT (Texas Instruments, Inc.) CONNECTOR ACCESSORY PDF資料下載

參數(shù)資料

| 型號: | HPC3130APBMQUADFLAT |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | CONNECTOR ACCESSORY |

| 中文描述: | 連接器附件 |

| 文件頁數(shù): | 36/41頁 |

| 文件大?。?/td> | 537K |

| 代理商: | HPC3130APBMQUADFLAT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當前第36頁第37頁第38頁第39頁第40頁第41頁

HPC3130A

PCI HOT PLUG CONTROLLER

SCPS055 – NOVEMBER 1999

36

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

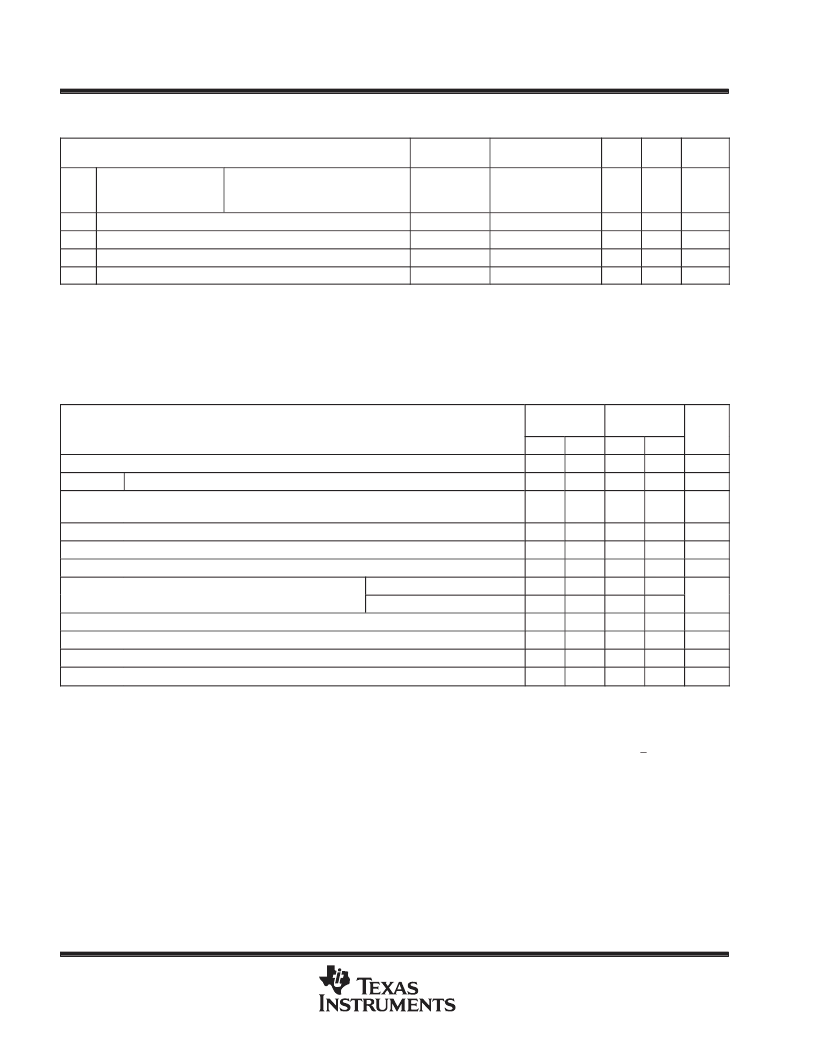

PCI timing requirements over recommended ranges of supply voltage and operating free–air

temperature

(see Note 3)

PARAMETER

ALTERNATE

SYMBOL

TEST CONDITIONS

MIN

MAX

UNITS

tpd

Propagation delay time

PCLK to shared signal valid delay

time

tval

CL = 50 pF,

See Note 4,

1,2,3

2

11

ns

ten

tdis

tsu

th

Applies to external output buffers.

NOTES:

3. This data sheet uses the following conventions to describe time ( t ) intervals. The format is: tA, where

subscript A

indicates the type

of dynamic parameter being represented. One of the following is used: tpd = propagation delay time, td = delay time, tsu = setup time,

and th = hold time.

4. PCI shared signals are AD31–AD0, C/BE3–C/BE0, PCIFRAME, PCITRDY, PCIIRDY, PCISTOP, IDSEL, PCIDEVSEL, and

PCIPAR.

Enable time, high-impedance-to-active delay time from PCLK

ton

toff

tsu

th

2

ns

Disable time, active-to-high-impedance delay time from PCLK

28

ns

Valid setup time, before PCLK

3,4

3

ns

Hold time, after PCLK high

4

0

ns

serial bus interface

STANDARD

MODE

FAST MODE

UNIT

MIN

MAX

MIN

MAX

fSCL

tBUF

SCL clock frequency (see Note 5)

0

100

0

400

kHz

μ

s

Bus free time between a STOP and START condition

4.7

1.3

tHD;STA

Hold time (repeated) START condition. After this period, the first clock pulse is

generated.

4

0.6

μ

s

tLOW

tHIGH

tSU;STA

LOW period of the SCL clock

4.7

1.3

μ

s

μ

s

μ

s

HIGH period of the SCL clock

4

0.6

Setup time for a repeated START condition

4.7

0.6

tHD;DAT

Data hold time (see Note 6)

For CBUS compatible masters:

5

μ

s

For serial bus devices:

01

250

01

0.92

tSU;DAT

tR

tF

tFSU;STO

All values refer to serial bus interface VIH MIN and VIL MAX levels

NOTES:

5. A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the VIH MIN of the SCL signal) in order

to bridge the undefined region of the falling edge of SCL.

6. The maximum tHD;DAT has only to be met if the device does not stretch the LOW period (tLOW ) of the SDL signal.

7. A fast mode serial bus device can be used in a standard mode serial bus system, but the requirement tSU;DAT > 250 ns must then

be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does

stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line tR MAX + tSU;DAT = 1000 + 250 = 1250 ns

(according to the Standard Mode Serial Bus Specification) before the SCL line is released.

Data setup time (see Note 7)

1003

20

μ

s

μ

s

μ

s

μ

s

Rise time of both SDA and SCL signals

1000

300

Fall time of both SDA and SCL signals

300

20

300

Setup time for STOP condition

4

0.6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HPC3130APGELOW-PROFILEQUA | Circular Connector; No. of Contacts:79; Series:MS27656; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:21; Circular Contact Gender:Socket; Circular Shell Style:Wall Mount Receptacle RoHS Compliant: No |

| HPC3130APBM | PCI Bus Interface/Controller |

| HPC3130APBKLOW-PROFILEQUA | DIODE ZENER DUAL COMMON-CATHODE 300mW 33Vz 5mA-Izt 0.0606 0.1uA-Ir 25 SOT-23 3K/REEL |

| HPC3130PGELOW-PROFILEQUAD | PCI HOT PLUG CONTROLLER |

| HPC3130PBMQUADFLAT | PCI HOT PLUG CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HPC3130APGE | 功能描述:外圍驅(qū)動器與原件 - PCI HOT PLUG CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| HPC3130APGEG4 | 功能描述:外圍驅(qū)動器與原件 - PCI HOT PLUG CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| HPC3130APGELOW-PROFILEQUA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:PCI HOT PLUG CONTROLLER |

| HPC3130PBK | 功能描述:外圍驅(qū)動器與原件 - PCI HOT PLUG CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| HPC3130PBKLOW-PROFILEQUAD | 制造商:TI 制造商全稱:Texas Instruments 功能描述:PCI HOT PLUG CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。