- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371807 > HFA3726IN (HARRIS SEMICONDUCTOR) 3.3V 288-mc CPLD PDF資料下載

參數(shù)資料

| 型號: | HFA3726IN |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 衰減器 |

| 英文描述: | 3.3V 288-mc CPLD |

| 中文描述: | 10 MHz - 400 MHz RF/MICROWAVE QUADRAPHASE MODEM |

| 文件頁數(shù): | 17/21頁 |

| 文件大小: | 162K |

| 代理商: | HFA3726IN |

17

The “I” and “Q” filter matching is within 2

o

for phase and 0.5dB

for amplitude at the passband. Group delay characteristics

follow closely a theoretical 5th order Butterworth design.

When in the receive mode, the filters exhibit a 0dB of gain

with differential inputs and single ended outputs.

In the transmit mode, the digital ground referenced “I” and

“Q” input signals are level shifted, shaped and buffered with

constant driving differential outputs of 550mV

P-P

.

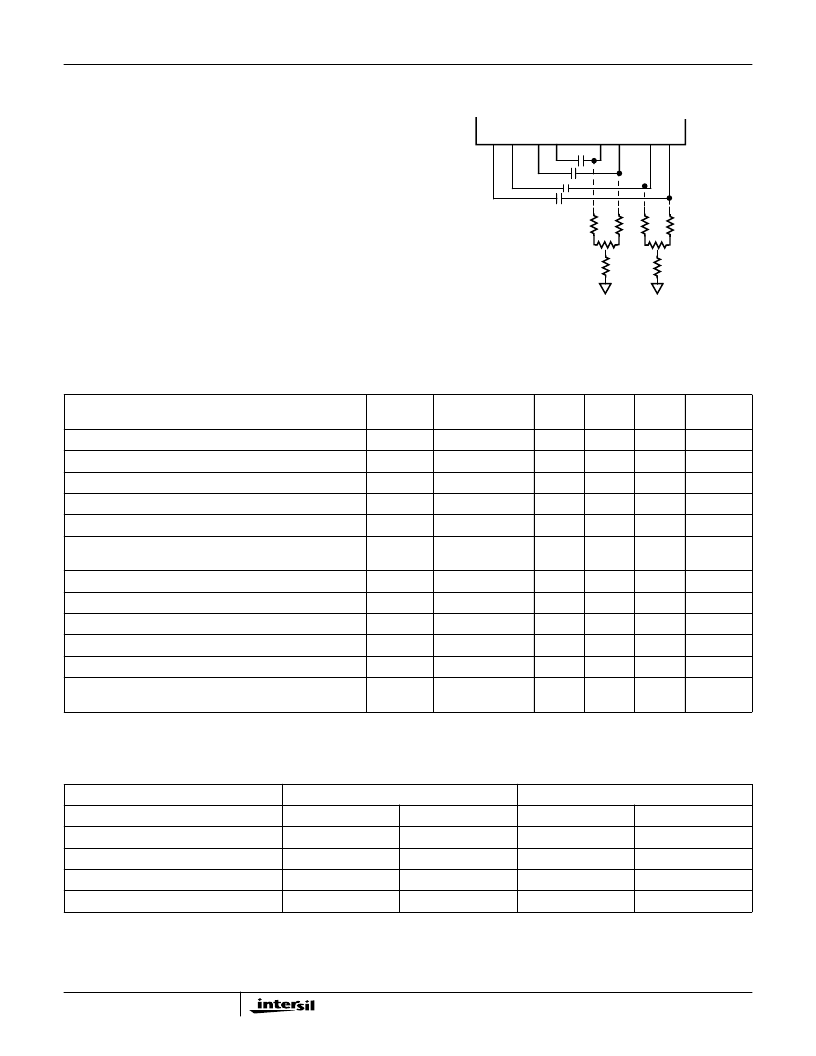

Coupling Capacitors

Capacitor coupling is used to tie all HFA3726 blocks together.

Special bias is used to maintain the DC levels on both ends of

coupling pins (capacitors) when the device is changes from

Transmitter to a Receiver and vice versa. The capacitance

values must be chosen as a compromise to maintain proper

frequency response and settling times (when the device is

brought up from sleep mode or power down).

1K

1K

1K

1K

43K

50K

43K

50K

M

M

M

M

40

39

38

37

FIGURE 25. CARRIER NULL BIASING

AC Electrical Specifications, IF Limiter, Single Stage Individual Performance

Full Supply Range, T

A

= 25

o

C

PARAMETER

SYMBOL

(NOTE 25)

TEST LEVEL

MIN

TYP

MAX

UNITS

IF Frequency Range (Min Limited by Bypass Capacitors)

IFf

A

-

-

400

MHz

IF Voltage Gain

IFvG

A

39

45

-

dB

IF Amp. Noise Figure at 250

Source Input

IFNF

B

-

-

7

dB

Maximum IF Input, Single Ended

IFinmax

B

-

-

500

mV

P-P

IF Differential Limiting Output (1st Harmonic at 500

Load)

IFVpp

A

160

200

260

mV

P-P

IF Voltage Output Variation at -40dBm to -10dBm Input Range,

500

Load

IFVppI

A

-0.5

-

+0.5

dB

RSSI Slope, Current Output

IFRSSIsi

B

5.7

-

μ

A/dB

RSSI Slope, Voltage Output at 6K Load

IFRSSIv

A

25

34

45

mV/dB

RSSI Output Voltage Compliance

IFRSSIvc

B

-

-

V

CC

-0.7

V

RSSI DC Offset and Noise Induced Voltage at 6K Load

IFRSSIof

A

200

400

600

mV

RSSI Absolute Accuracy, V

IN

= -40dBm

IFRSSIa

A

-10

-

+10

%

RSSI Rise and Fall Time at 50pF Load

(-20dBm to -40dBm Input)

IFRSSIt

B

-

-

1

μ

s

NOTE:

25. A = Production Tested, B = Based on Characterization, C = By Design

TABLE 3. IF LIMITER S11, S22 PARAMETER

FREQUENCY

S11 (SINGLE ENDED)

S22 (DIFFERENTIAL)

50MHz

0.96

-4.0

o

0.45

0.0

o

100MHz

0.95

-8.0

o

0.45

3.0

o

200MHz

0.91

-17.0

o

0.47

7.0

o

300MHz

0.84

-26.0

o

0.50

9.0

o

400MHz

0.80

-33.0

o

0.53

10.0

o

HFA3726

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HFA3765IA | AGC and Quadrature IF Demodulator |

| HFA3765 | AGC and Quadrature IF Demodulator |

| HFA3765IA96 | AGC and Quadrature IF Demodulator |

| HFA3766IN96 | 400MHz AGC Quadrature IF Modulator/Demodulator |

| HFA3766IN | 400MHz AGC Quadrature IF Modulator/Demodulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HFA3726IN WAF | 制造商:Harris Corporation 功能描述: |

| HFA3726IN96 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HFA3761 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:400MHz AGC and Quadrature IF Demodulator |

| HFA3761/3763IN WAF | 制造商:Harris Corporation 功能描述: |

| HFA3761IN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:400MHz AGC and Quadrature IF Demodulator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。