- 您現在的位置:買賣IC網 > PDF目錄370459 > HD404618H (Hitachi,Ltd.) 4-Bit Single-Chip Microcomputer PDF資料下載

參數資料

| 型號: | HD404618H |

| 廠商: | Hitachi,Ltd. |

| 英文描述: | 4-Bit Single-Chip Microcomputer |

| 中文描述: | 4位單片機 |

| 文件頁數: | 45/89頁 |

| 文件大小: | 358K |

| 代理商: | HD404618H |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

HD404618 Series

45

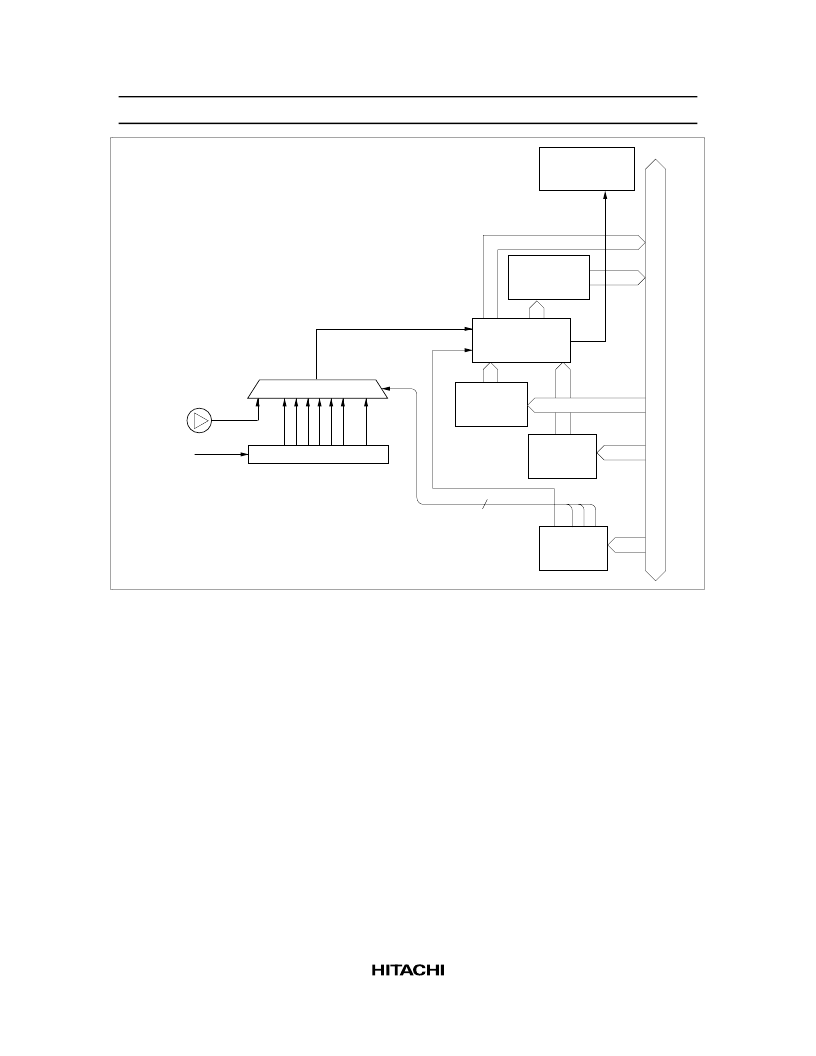

System

clock

INT

1

Selector

Prescaler S (PSS)

Clock

Timer counter register BU (TCBU)

Timer counter

register BL

(TCBL)

Timer counter B

(TCB)

Timer load

register BU

(TLRU)

Timer load

register BL

(TLRL)

Timer mode

register B

(TMB)

Timer B interrupt

request flag

(IFTB)

f

cyc

/f

SUB

(t

cyc

/t

subcyc

)

3

I

2

÷

4

÷

8

÷

3

÷

1

÷

5

÷

2

÷

Free-running

control

Overflow

Figure 27 Timer B Block Diagram

Timer C (TCCL and TCRL: $00E, TCCU and TCRU: $00F):

Eight-bit write-only timer load register

(TCRL and TCRU) and read-only timer counter (TCCL and TCCU) located at the same addresses. The

eight-bit configuration consists of lower and upper 4-bit digits located at sequential addresses. The

operation of timer C is basically the same as that of timer B.

The auto-reload function and prescaler division ratio of timer C depend on the state of timer mode register

C (TMC). Timer C is initialized to the value set in TMC by software, and is then incremented by one at

each clock input. If an input is applied to timer C after it has reached $FF, an overflow is generated. In

this case, if the auto-reload function is enabled, timer C is initialized to its initial value; if auto-reload is

disabled, the timer is initialized to $00. The overflow sets the timer C interrupt request flag (IFTC: $002,

bit 2).

Timer C also functions as a watchdog timer. If a program routine runs out of control and an overflow is

generated while the watchdog on (WDON) flag is set, the MCU is reset. This error can be detected by

having the program control timer C reset before timer C reaches $FF.

The WDON can only have 1 written to it ; it is cleared to 0 only by MCU reset.

Timer Mode Register A (TMA: $008):

Four-bit write-only register that controls timer A as shown in

table 21.

相關PDF資料 |

PDF描述 |

|---|---|

| HD404618TF | 4-Bit Single-Chip Microcomputer |

| HD4074618 | 4-Bit Single-Chip Microcomputer |

| HD4074618FS | CONNECTOR |

| HD4074618H | 4-Bit Single-Chip Microcomputer |

| HD4074618TF | 4-Bit Single-Chip Microcomputer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HD404618SERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| HD404618TF | 制造商:HITACHI 制造商全稱:Hitachi Semiconductor 功能描述:4-Bit Single-Chip Microcomputer |

| HD4046212FS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4-Bit Microcontroller |

| HD4046212H | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4-Bit Microcontroller |

| HD4046212R | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:AS Microcomputer Incorporating a DTMF Generator Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復。