- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370450 > HCPL-2602 High CMR Line Receiver Optocouplers(高共態(tài)抑制線(xiàn)接收光耦器) PDF資料下載

參數(shù)資料

| 型號(hào): | HCPL-2602 |

| 英文描述: | High CMR Line Receiver Optocouplers(高共態(tài)抑制線(xiàn)接收光耦器) |

| 中文描述: | 高CMR線(xiàn)接收光耦合器(高共態(tài)抑制線(xiàn)接收光耦器) |

| 文件頁(yè)數(shù): | 9/16頁(yè) |

| 文件大小: | 263K |

| 代理商: | HCPL-2602 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

9

7. CM

is the maximum tolerable rate of rise of the common mode voltage to assure that the output will remain in a high logic state

(i.e., V

> 2.0 V).

8. CM

L

is the maximum tolerable rate of fall of the common mode voltage to assure that the output will remain in a low logic state (i.e.,

V

< 0.8 V).

9. For sinusoidal voltages,

CM

|

|dv

=

π

f

CM

V

CM

(p-p)

dt

max

10. No external pull up is required for a high logic state on the enable input. If the V

E

pin is not used, tying V

E

to V

CC

will result in

improved CMR performance.

11. In accordance with UL 1577, each optocoupler is proof tested by applying an insulation test voltage of

≥

3000 for one second

(leakage detection current limit, I

≤

5

μ

A).

12. t

is equal to the worst case difference in t

PHL

and/or t

PLH

that will be seen between units at any given temperature within the

operating condition range.

13. See application section titled “Propagation Delay, Pulse-Width Distortion and Propagation Delay Skew” for more information.

Notes:

1. Bypassing of the power supply line is required, with a 0.1

μ

F ceramic disc capacitor adjacent to each optocoupler as illustrated in

Figure 15. Total lead length between both ends of the capacitor and the isolator pins should not exceed 20 mm.

2. Device considered a two terminal device: pins 1, 2, 3, and 4 shorted together, and pins 5, 6, 7, and 8 shorted together.

3. The t

propagation delay is measured from the 3.75 mA point on the falling edge of the input pulse to the 1.5 V point on the rising

edge of the output pulse.

4. The t

propagation delay is measured from the 3.75 mA point on the rising edge of the input pulse to the 1.5 V point on the falling

edge of the output pulse.

5. The t

enable propagation delay is measured from the 1.5 V point on the falling edge of the enable input pulse to the 1.5 V point

on the rising edge of the output pulse.

6. The t

enable propagation delay is measured from the 1.5 V point on the rising edge of the enable input pulse to the 1.5 V point on

the falling edge of the output pulse.

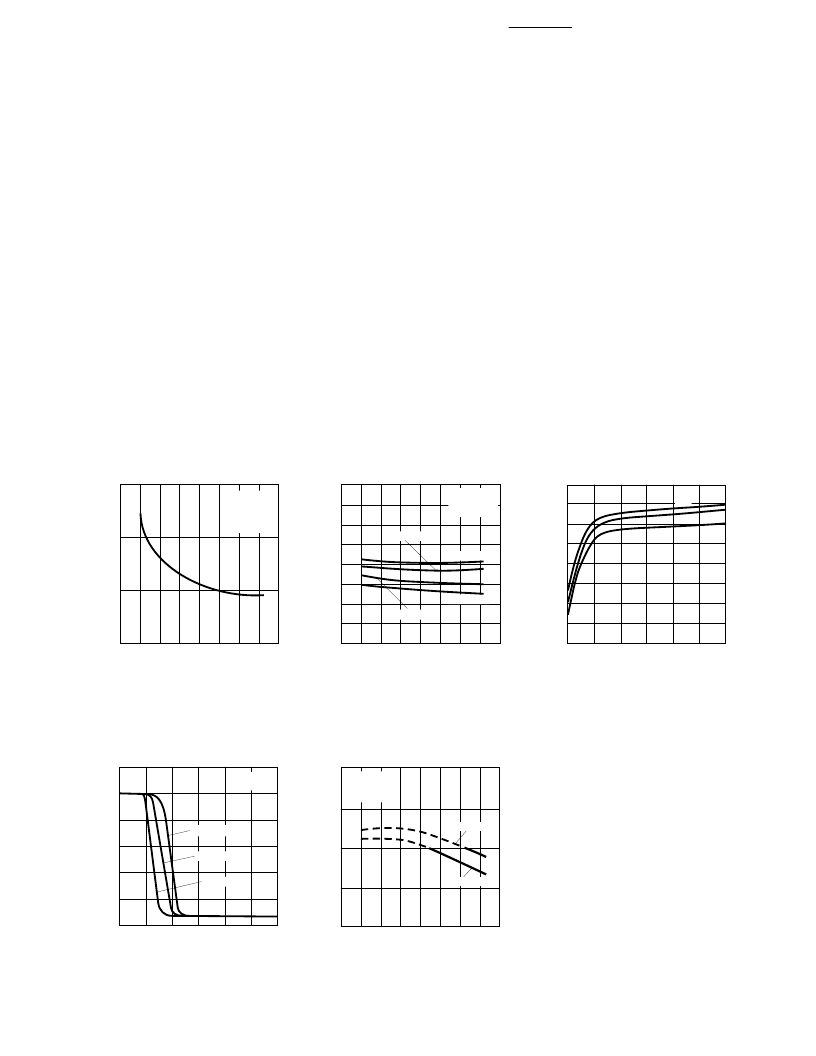

Figure 1. Typical High Level Output

Current vs. Temperature.

Figure 2. Typical Low Level Output

Voltage vs. Temperature.

Figure 3. Typical Input Characteristics.

1.0

0

20

30

40

60

I

I

– INPUT CURRENT – mA

10

50

1.2

1.4

1.6

1.8

2.0

2.2

2.4

2.6

V

I

25°C

70°C

0°C

Figure 5. Typical Low Level Output

Current vs. Temperature.

Figure 4. Typical Output Voltage vs.

Forward Input Current.

1

6

2

3

4

5

1

2

3

4

5

6

I

F

– FORWARD INPUT CURRENT – mA

R

L

= 350

R

L

= 1 K

R

L

= 4 K

00

V

CC

= 5 V

T

A

= 25 °C

V

O

I

O

–

-60

0

T

A

– TEMPERATURE – °C

100

10

15

-20

5

20

V

CC

= 5.5 V

V

O

= 5.5 V

V

= 2 V

I

I

= 250 μA

60

-40

0

40

80

V

CC

= 5.5 V

V

= 2 V

I

I

= 5 mA

0.5

0.4

-60

-20

20

60

100

T

A

– TEMPERATURE – °C

0.3

80

40

0

-40

0.1

V

O

0.2

I

O

= 16 mA

I

O

= 12.8 mA

I

O

= 9.6 mA

I

O

= 6.4 mA

V

CC

= 5 V

V

E

= 2 V

V

OL

= 0.6 V

70

60

-60

-20

20

60

100

T

A

– TEMPERATURE – °C

50

80

40

0

-40

20

I

O

40

I

I

= 10-15 mA

I

I

= 5.0 mA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HCPL-261A | HCMOS Compatible, High CMR, 10 MBd Optocouplers |

| HCPL-261N | High CMR, High Speed TTL Compatible Optocouplers |

| HCPL-2630 | High CMR, High Speed TTL Compatible Optocouplers |

| HCPL-2631 | High CMR, High Speed TTL Compatible Optocouplers |

| HCPL-263A | High CMR, High Speed TTL Compatible Optocouplers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HCPL-2602#300 | 功能描述:高速光耦合器 1Ch 5mA 600mW RoHS:否 制造商:Avago Technologies 電流傳遞比: 最大波特率: 最大正向二極管電壓:1.75 V 最大反向二極管電壓:5 V 最大功率耗散:40 mW 最大工作溫度:+125 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-5 封裝:Tube |

| HCPL-2602#500 | 功能描述:高速光耦合器 1Ch 5mA 600mW RoHS:否 制造商:Avago Technologies 電流傳遞比: 最大波特率: 最大正向二極管電壓:1.75 V 最大反向二極管電壓:5 V 最大功率耗散:40 mW 最大工作溫度:+125 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-5 封裝:Tube |

| HCPL-2602-000E | 功能描述:高速光耦合器 1Ch 5mA 600mW RoHS:否 制造商:Avago Technologies 電流傳遞比: 最大波特率: 最大正向二極管電壓:1.75 V 最大反向二極管電壓:5 V 最大功率耗散:40 mW 最大工作溫度:+125 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-5 封裝:Tube |

| HCPL2602300E | 制造商:Avago Technologies 功能描述: |

| HCPL-2602-300E | 功能描述:高速光耦合器 1Ch 5mA 600mW RoHS:否 制造商:Avago Technologies 電流傳遞比: 最大波特率: 最大正向二極管電壓:1.75 V 最大反向二極管電壓:5 V 最大功率耗散:40 mW 最大工作溫度:+125 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-5 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。