- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄353457 > HC646 (National Semiconductor Corporation) Non-Inverting Octal Bus Transceiver/Registers PDF資料下載

參數(shù)資料

| 型號(hào): | HC646 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | Non-Inverting Octal Bus Transceiver/Registers |

| 中文描述: | 非反相八路總線(xiàn)收發(fā)器/寄存器 |

| 文件頁(yè)數(shù): | 5/12頁(yè) |

| 文件大小: | 91K |

| 代理商: | HC646 |

September 1993

2

Philips Semiconductors

Product specication

Octal bus transceiver/register; 3-state

74HC/HCT646

FEATURES

Independent register for A and B buses

Multiplexed real-time and stored data

Output capability: bus driver

ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT646 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT646 consist of bus transceiver circuits with

3-state outputs, D-type flip-flops, and control circuitry

arranged for multiplexed transmission of data directly from

the internal registers. Data on the “A” or “B” bus will be

clocked into the registers as the appropriate clock

(CPAB and CPBA) goes to a HIGH logic level. Output

enable (OE) and direction (DIR) inputs are provided to

control the transceiver function. In the transceiver mode,

data present at the high-impedance port may be stored in

either the “A” or “B” register, or in both. The select source

inputs (SAB and SBA) can multiplex stored and real-time

(transparent mode) data. The direction (DIR) input

determines which bus will receive data when OE is active

(LOW). In the isolation mode (OE = HIGH), “A” data may

be stored in the “B” register and/or “B” data may be stored

in the “A” register.

When an output function is disabled, the input function is

still enabled and may be used to store and transmit data.

Only one of the two buses, A or B, may be driven at a time.

The “646” is functionally identical to the “648”, but has

non-inverting data paths.

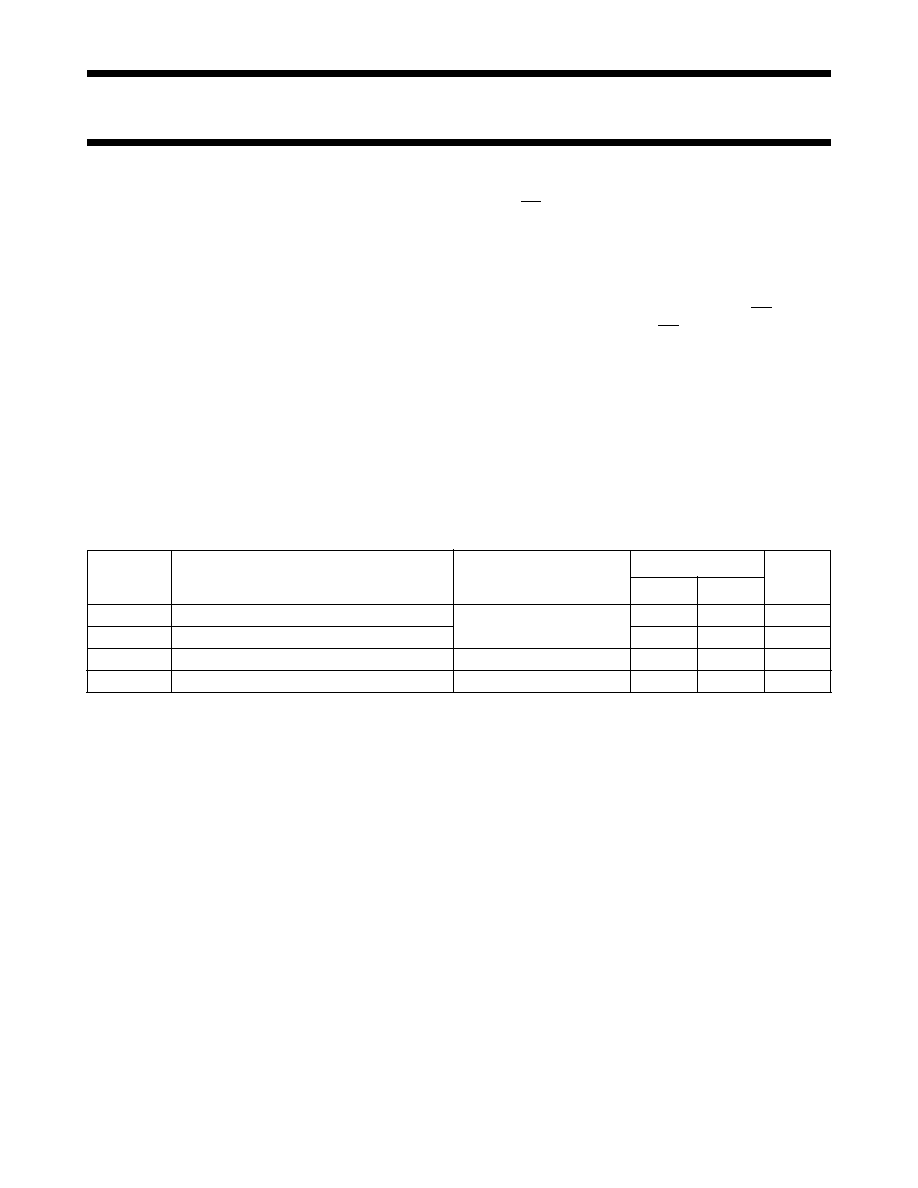

QUICK REFERENCE DATA

GND = 0 V; Tamb =25 °C; tr =tf = 6 ns

Notes

1. CPD is used to determine the dynamic power dissipation (PD in W):

PD =CPD × VCC2 × fi + ∑ (CL × VCC2 × fo) where:

fi = input frequency in MHz

fo = output frequency in MHz

∑ (CL × VCC2 × fo) = sum of outputs

CL = output load capacitance in pF

VCC = supply voltage in V

2. For HC the condition is VI = GND to VCC

For HCT the condition is VI = GND to VCC 1.5 V

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

HC

HCT

tPHL/ tPLH

propagation delay

An, Bn to Bn, An

CL = 15 pF; VCC =5V

11

13

ns

fmax

maximum clock frequency

69

85

MHz

CI

input capacitance

3.5

pF

CPD

power dissipation capacitance per channel

notes 1 and 2

30

33

pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HPC46400EVHG2 | High-Performance Communications MicroController |

| HPC46400EVHG20 | High-Performance Communications MicroController |

| HPC167064EL20 | High-Performance microController with a 16k UV Erasable CMOS EPROM |

| HCT273 | Octal D Flip-Flop with Common Clock and Reset with LSTTL-Compatible Inputs |

| H11A1 | 6-Pin DIP Optoisolators Transistor Output |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HC64R8 | 制造商:CONNOR-WINFIELD 制造商全稱(chēng):Connor-Winfield Corporation 功能描述:14 PIN DIP HCMOS/TTL COMPATIBLE |

| HC64R8R | 制造商:CONNOR-WINFIELD 制造商全稱(chēng):Connor-Winfield Corporation 功能描述:HCMOS/TTL COMPATIBLE TRI-STATE OUTPUT |

| HC64R8RG | 制造商:CONNOR-WINFIELD 制造商全稱(chēng):Connor-Winfield Corporation 功能描述:5.0V 14 Pin DIP HCMOS Clock Oscillator |

| HC64R8RG-49.408M | 制造商:CONNOR-WINFIELD 制造商全稱(chēng):Connor-Winfield Corporation 功能描述:5.0V 14 Pin DIP HCMOS Clock Oscillator |

| HC64RA | 制造商:CONNOR-WINFIELD 制造商全稱(chēng):Connor-Winfield Corporation 功能描述:14 PIN DIP 3.3V HCMOS TRI-STATE E/D |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。