- 您現在的位置:買賣IC網 > PDF目錄371771 > HB28L064RM3 (Renesas Technology Corp.) MultiMediaCard 32 MByte/64 MByte/128 MByte/256 MByte/512 MByte PDF資料下載

參數資料

| 型號: | HB28L064RM3 |

| 廠商: | Renesas Technology Corp. |

| 英文描述: | MultiMediaCard 32 MByte/64 MByte/128 MByte/256 MByte/512 MByte |

| 中文描述: | 多媒體32 MByte/64 MByte/128 MByte/256 MByte/512字節(jié) |

| 文件頁數: | 59/91頁 |

| 文件大小: | 526K |

| 代理商: | HB28L064RM3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁當前第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁

HB28K032/L064/J128/J256/J512MM3, HB28K032/L064/J128/J256RM3

Rev.0.02, Sep.15.2004, page 59 of 89

Erase and Write Protect Management

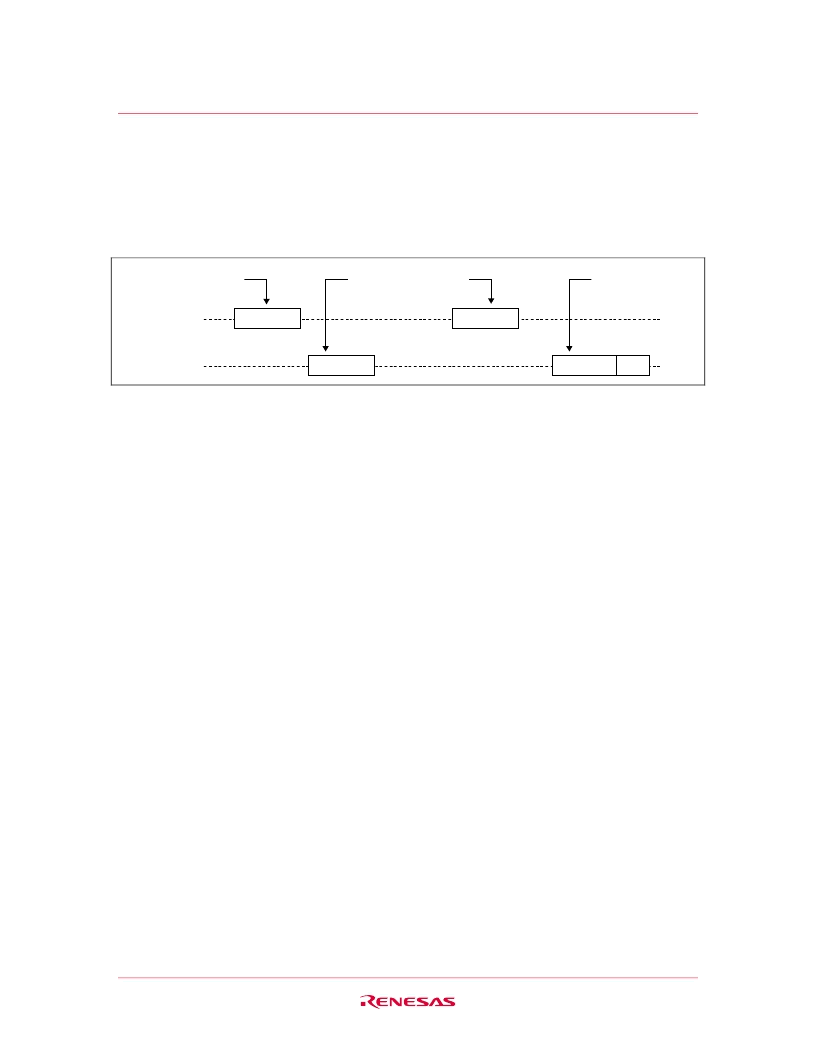

The erase and write protect management procedures in the SPI mode are identical to those of the

MultiMediaCard mode. While the card is erasing or changing the write protection bits of the predefined

sector list, it will be in a busy state and hold the DataOut line low. Figure

“

No Data Operations

”

illustrates

a

‘

no data

’

bus transaction with and without busy signaling.

Data in

Data out

command

response

response busy

command

from

host

to card

from

card

to host

from

card

to host

from

host

to card

‘No Data’ Operations

Reading CID/CSD Registers

Unlike the MultiMediaCard protocol (where the register contents are sent as a command response), reading

the contents of the CSD and CID registers in SPI mode is a simple read-block transaction. The card will

respond with a standard response token (refer to Figure

“

Read Operation

”

) followed by a data block of 16

bytes suffixed with a 16-bit CRC. The data timeout for the CSD command cannot be set to the card TAAC

since this value is stored in the CSD. Therefore the standard response timeout value (N

CR

) is used for read

latency of the CSD register.

Reset Sequence

The MultiMediaCard requires a defined reset sequence. After power on reset or CMD0 (software reset) the

card enters an idle state. At this state the only legal host command is CMD1 (SEND_OP_COND) and

CMD58 (READ_OCR). In SPI mode, as opposed to MultiMediaCard mode, CMD1 has no operands and

does not return the contents of the OCR register. Instead, the host may use CMD58 (available in SPI mode

only) to read the OCR register. Furthermore, it is in the responsibility of the host to refrain from accessing

cards that do not support its voltage range. The usage of CMD58 is not restricted to the initializing phase

only, but can be issued at any time. The host must poll the card (by repeatedly sending CMD1) until the

‘

in-idle-state

’

bit in the card response indicates (by being set to 0) that the card completed its initialization

processes and is ready for the next command. The host must poll the card (by repeatedly sending CMD1)

until the

‘

in-idle-state

’

bit in the card response indicates (by being set to 0) that the card completed its

initialization processes and is ready for the next command.

相關PDF資料 |

PDF描述 |

|---|---|

| HB28K032MM3 | MultiMediaCard 32 MByte/64 MByte/128 MByte/256 MByte/512 MByte |

| HB28K032RM3 | MultiMediaCard 32 MByte/64 MByte/128 MByte/256 MByte/512 MByte |

| HB28L064MM3 | MultiMediaCard 32 MByte/64 MByte/128 MByte/256 MByte/512 MByte |

| HB28J512MM3 | MultiMediaCard 32 MByte/64 MByte/128 MByte/256 MByte/512 MByte |

| HB3104AD | 128Kx8 EEPROM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HB2A102K-S265B | 制造商:Hitano Enterprise Corp 功能描述:Bulk |

| HB2A102K-S565B | 制造商:Hitano Enterprise Corp 功能描述:Bulk |

| HB2A103K-S565B | 制造商:Hitano Enterprise Corp 功能描述: |

| HB2A122K-S265B | 制造商:Hitano Enterprise Corp 功能描述: |

| HB2A122K-S565B | 制造商:Hitano Enterprise Corp 功能描述:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。